- 680x0

-

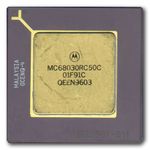

Motorola 680x0

En informatique et électronique, on appelle informellement Motorola 680x0 ou M68k ou 68k, la famille de microprocesseurs CISC compatibles avec l'architecture du Motorola 68000 : les principaux membres étant les Motorola 68000, 68020, 68030, 68040 et 68060. Dans les années 1980, cette famille était souvent comparée à la famille x86 d'Intel et considérée comme concurrente.

Les microprocesseurs m68k ont notamment équipé tous les Macintosh des années 1980, tous les Amiga, les Atari ST, la Sega Megadrive et de nombreuses stations de travail, dont les premières de Sun Microsystems.

Sommaire

Les différents processeurs de la famille

- première génération : 68000, 68EC000, 68HC000, 68008, 68010, 68012

- deuxième génération : 68020, 68EC020, 68030, 68EC030

- troisième génération : 68040, 68EC040, 68LC040

- quatrième génération : 68060

- autres : 68330 (ou CPU32), Dragonball, Coldfire

Motorola a précisé lors du passage direct du 68040 au 68060 que les chiffres de dizaine impairs (68010, 68030 et l'inexistant 68050) étaient utilisés pour des améliorations minimes, pas pour des révisions complètes de la microarchitecture (longueur du pipeline, nombre de pipelines, etc.). Le 68050 n'existe donc pas car Motorola n'a pas produit d'amélioration partielle du 68040.

Modes de fonctionnement

Les 680x0 ont un adressage linéaire sur 32 bits. Ils n'ont pas de mode d'adressage particulier pour les registres d'entrée-sortie.

Les 680x0 peuvent fonctionner en mode utilisateur ou superviseur. En mode utilisateur, certaines instructions ne sont pas autorisées et déclenchent une exception. Le mode superviseur est conçu pour permettre de faire fonctionner une machine virtuelle 680x0.

Jeu d'instructions

La famille 680x0 a un jeu d'instructions CISC qui a atteint sept types de données (sans compter les types flottants) et 18 modes d'adressages à partir du Motorola 68020 ; cela sans compter le coprocesseur arithmétique.

Registres

La famille 680x0 est basée sur des registres 32 bits.

- 8 registres de données notés

D0àD7. - 8 registres d'adresse notés

A0àA7.- Le registre

A7est le pointeur de pile, aussi notéSP. - Il existe en fait deux pointeurs de pile : USP et SSP. USP est la pile utilisée en mode utilisateur, tandis que SSP est la pile utilisée en mode superviseur.

- Le registre

Les registres d'adresse ne peuvent être utilisés que pour les opérations arithmétiques simples comme l'addition et la soustraction. Leur utilisation est en revanche obligatoire dans de nombreux modes d'adressage de la mémoire.

Codes de condition

Les instructions arithmétiques et logiques et les copies positionnent automatiquement les bits de conditions, sauf lorsque la destination est un registre d'adresse. Il existe 5 bits de condition :

N(negative) : indique si le bit de poids fort du résultat est 1Z(zero) : indique si le résultat est nulV(overflow) : indique si le calcul a causé un débordement arithmétiqueC(carry) : bit de retenueX(extend) : n'est pas modifié par les copies, autrement prend la même valeur que C

Instructions

Les instructions sont de longueur variable, par multiples de 16 bits. La plupart des instructions prend une ou deux opérandes. Les instructions qui produisent un résultat à partir de deux opérandes sauvent le résultat dans la seconde opérande source ; par exemple :

ADD.L D2,D3additionneD2àD3et enregistre le résultat dansD3.Les instructions courantes sont supportées : addition, soustraction, multiplication, division, addition et soustraction BCD, opérateurs logiques, manipulation de bit individuel, décalages et rotations de bits, sauts, sauts conditionnels, appel et retour de sous-routine. Parmi les instructions plus originales, on trouve :

MOVEM: transfert de 1 à tous les registres, sélectionnés par un masque de bits, avec la mémoireDBcc: décrémentation d'un registre et branchement conditionnelLINKetUNLK: mise à jour du frame pointer

À partir du 68020, on trouve des instructions sur les champs de bits.

Taille des opérandes

Les processeurs de la famille 680x0 peuvent travailler sur divers types d'opérandes : bit, champ de bits (à partir du 68020), octet, mot de 16 bits, mot long de 32 bits, quadruple mot de 64 bits (à partir du 68020) et entier BCD.

Sur le Motorola 68000 les accès mémoire doivent être alignés sur 16 bits. À partir du Motorola 68020, les accès non alignés sont supportés.

Mode d'adressage

Les modes d'adressage standards sont :

Dn: registre de donnée NAn: registre d'adresse N(An): adresse = An(An)+: adresse = An, An est post-incrémenté-(An): adresse = An, An est pré-décrémenté(d16,An): adresse = d16 + An(d8,An,Xn): adresse = d8 + An + Xn(bd,An,Xn)(à partir du 68020) : adresse = bd + An + Xn([bd,An],Xn,od)(à partir du 68020) : adresse = adresse dans (bd + An) + Xn + od([bd,An,Xn],od)(à partir du 68020) : adresse = adresse dans (bd + An + Xn) + od(d16,PC): adresse = d16 + PC(d8,PC,Xn): adresse = d8 + PC + Xn([bd,PC],Xn,od)(à partir du 68020) : adresse = adresse dans (bd + An) + Xn + od([bd,PC,Xn],od)(à partir du 68020) : adresse = adresse dans (bd + An + Xn) + od(xxx).W: adresse de 16 bits signés(xxx).L: adresse de 32 bits signés#<data>: donnée immédiate de 8, 16 ou 32 bits, valable seulement comme source

Avec :

- d8, d16 : déplacement signé de 8, respectivement 16 bits

- Xn : registre An ou Dn, auquel on prend 16 ou 32 bits signés, et qu'on multiplie par 1, 2, 4 ou 8 avant l'addition

- bd, od : déplacement optionnel signé de 16 ou 32 bits

- PC = compteur ordinal

Les modes d'adressage du 68020 de la forme

([bd,An],Xn,od)utilisent une double indirection : une première adresse est calculée, dans laquelle on lit une seconde adresse pour ensuite calculer l'adresse finale.Utilisation

Par Apollo Computer

Pour ses stations de travail durant les années 1980.

Par Apple

Apple a utilisé les processeurs 68000 dans le Lisa puis les premiers Macintosh (Macintosh 128K, Mac 512K, Mac Plus, Mac SE et Classic).

Les machines suivantes (Macintosh LC et Macintosh II) furent équipés de processeurs 68020, puis les Macintosh IIcx, IIci, IIfx, LC III et SE/30 furent équipés de 68030.

Enfin, les Quadra et derniers LC (LC 475, LC 630) eurent des processeurs 68040 (à noter que ces derniers LC n'eurent droit qu'à une version dépourvue de coprocesseur mathématique et dénommée 68LC040).

Avec l'arrivée d'une nouvelle génération de micro-ordinateurs Macintosh, connus sous le nom de Power Macintosh, Apple dota ses machines de processeurs PowerPC, conçus en commun avec Motorola et IBM.

Par Atari

Dans sa gamme Atari ST, comprenant également le STE, le MegaST et MegaSTE. Le TT030 et le Falcon comprenaient un 68030.

Par Commodore

Dans la gamme Amiga:

- 68000: dans les Amiga 500, 600, 1000 et 2000

- 68EC020: dans la console de jeu CD32 et Amiga 1200

- 68030: dans l'Amiga 3000

- 68EC030 ou 68040: dans l'Amiga 4000

- 68881: comme processeur arithmétique dans les Amiga 3000 et 4000.

les processeurs 68020, 68030, 68040 et 68060 étaient disponibles en kit pour la plupart des modèles Amiga.

Par NeXT

Les machines NeXT utilisaient des processeurs 68030 et 68040.

Par Palm

Le processeur DragonBall des Palm de première génération (et des autres systèmes sous Palm OS produits par Handspring, IBM, Sony, TRGPro, Qualcomm, Symbol...) est dérivé du 68000. Les Palm plus récents utilisent des processeurs ARM.

Par Sega

Pour la console Megadrive.

Par Silicon Graphics

Pour ses stations de travail, avant d'utiliser des microprocesseurs MIPS.

Par Sinclair

Le Sinclair QL utilisa la variante 68008 à bus 8 bits.

Par SNK

Pour la console Neo-Geo AES. Pour le système d'arcade Neo-Geo MVS.

Par Sun Microsystems

Pour ses stations de travail (Sun 1, 2 puis 3), avant d'utiliser des microprocesseurs SPARC.

Par Texas Instruments

Pour les calculatrices TI-89, TI-89 Titanium, TI-92, TI-92 Plus et TI Voyage 200.

Voir aussi

Liste des microprocesseurs Motorola

CPU 8 bits : 6800 • 6809 • CPU architecture RISC : 88000 CPU architecture 68000 : 68000 • 68008 • 68010 • 68012 • 68020 • 68030 • 68040 • 68060 • DragonBall • ColdFire CPU architecture PowerPC : 601 (G1) • 603 (G2) • PowerPC G3 • PowerPC G4 FPU : 68881/2 • MMU : 68851 DSP : DSP560XX • DSP563XX • DSP566XX • DSP568XX • DSP96XXX Catégorie : Microprocesseur 68000

Wikimedia Foundation. 2010.