- 68000

-

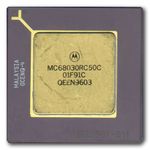

Motorola 68000

Apparu en 1979, le Motorola 68000 est un microprocesseur CISC 16/32 bits développé par Motorola. C'est le premier de la famille de microprocesseurs souvent appelée m68k ou 680x0, qui comprend notamment les microprocesseurs Motorola 68010, Motorola 68020, Motorola 68030, Motorola 68040 et Motorola 68060. Le nom du 68000 vient à la fois de la continuité avec la famille de microprocesseurs Motorola 6800 et du nombre de transistors qu'il contient, un peu plus de 68 000.

Sommaire

Architecture

Même si l'on a essentiellement retenu l'élargissement et la multiplication des registres disponibles, ainsi que l'introduction d'une certaine orthogonalité dans le jeu d'instruction, la principale innovation de la série 68000 par rapport à son prédecesseur, le Motorola 6809, réside dans l'apparition d'instructions privilégiées et des niveaux de fonctionnement utilisateur - superviseur. Cette distinction est fondamentale dans les systèmes d'exploitation modernes tels Unix, qui n'auraient pu que difficilement voir le jour sur ces plates-formes sans cette innovation.

A noter la présence de l'instruction TAS (Test And Set) qui permet de tester et modifier la valeur d'un octet en mémoire en une seule instruction non interruptible. Ce type d'instruction est indispensable pour implémenter les sémaphores utilisés pour la communication inter-processus, donc les systèmes d'exploitation multitâches.

Deux petits défauts, corrigés dans le Motorola 68010, rendent cependant le 68000 incapable de bien supporter la virtualisation et la mémoire virtuelle : L'instruction MOVE from SR permet de lire la partie superviseur du registre SR même en mode utilisateur, ce qui empêche sa virtualisation ; il n'est pas possible de relancer une instruction qui a causé une erreur d'accès à la mémoire, ce qui empêche la reprise d'un programme après avoir chargé les données manquantes.

16/32 bits

Le 68000 est qualifié de 16/32 bits car ses registres ont une largeur de 32 bits et ses instructions acceptent des données de 8, 16 et 32 bits. Toutefois, l'ALU (Unité arithmétique et logique) a une largeur de 16 bits, ce qui fait que les opérations sur 32 bits prennent plus de cycles d'horloge pour être exécutées. En outre, les bus externes ont une largeur de 16 bits pour les données et de 24 bits les adresses.

Espace mémoire

Le 68000 peut également adresser de façon linéaire un espace mémoire total de 16 méga-octets.

Cet espace mémoire peut être séparé en quatre parts (programme superviseur, données superviseur, programme utilisateur, données utilisateur) sans utilisation de circuit externe, mais par simple décodage de trois lignes d'état fournies par le processeur.

Ces trois bits apportent un grande sécurité matérielle des données et permettent d'étendre l'espace mémoire à 64 méga-octets.

Le 68000 est également particulièrement adapté à une configuration multiprocesseurs.

Il peut être aussi utilisé avec les circuit périphériques de première génération (PIA MC6821 par exemple) grâce à des signaux de synchronisation disponibles sur le bus.

Le 68000 est big endian.Registres du 68000

- 8 registres de données 32 bits :

- D0, D1, D2, D3, D4, D5, D6, D7

- 7 registres d'adresse 32 bits :

- A0, A1, A2, A3, A4, A5, A6

- le 8e registre d'adresse est le pointeur de pile correspondant au mode d'exécution utilisateur ou superviseur (USP ou SSP)

- A7 ou SP

- 4 registres spéciaux :

- PC (compteur ordinal 32 bits)

- SR (registre d'état 16 bits, l'octet de poids faible est appelé CCR)

- USP (pointeur de pile utilisateur 32 bits)

- SSP (pointeur de pile superviseur 32 bits)

Registre d'état et registre de codes conditions

Registre de Codes Condition CCR et Registre d'état SR:

Le registre d'état SR 16 bits se compose de deux octets distincts:

Poids faible : Octet utilisateur (CCR). Poids fort : Octet superviseur.Ce registre reflète l'état du processeur après chaque instruction, ce qui permet d'autoriser ou interdire les interruptions, ou tester le résultat d'une opération pour un branchement conditionnel par exemple.

Détail du SR et du CCR: b15 b0 T.S..III...XNZVC ________________ SR ________ CCROctet Superviseur: T: mode Trace S: état Superviseur I: masque d'Interruption 2 I: masque d'Interruption 1 I: masque d'Interruption 0 Octet Utilisateur CCR: X: bit d'eXtension N: bit de signe (Negative) Z: bit de Zero V: bit de débordement (oVerflow) C: bit de retenue (Carry)En mode Utilisateur, on ne peut écrire que dans le CCR. En mode Superviseur, on peut écrire dans tout le SR.

Modes d'adressage

Les différents modes d'adressage sont:

Adressage Immédiat:MOVE.W #$1000, A0 La valeur $1000 est mise dans A0 ADD.B #$C2, $2000 La valeur $C2 est ajoutée au contenu de la case $2000

Adressage Immédiat rapide (Quick):ADDQ #$04, D0 Comme adressage immédiat, mais sur 8 bits

Adressage Registre de Données:MOVE.B D1, $1000 Un des opérandes est un registre Dn NOT D0

Adressage Registre d'adresse:MOVE A0, D0 Un des opérandes est un registre An MOVE D0, A0

Adressage Registre Implicite:RTS Aucun registre n'est spécifié

Adressage Absolu Court:MOVE.B $1200, D0 Le contenu de la case $1200 est mis dans D0

Adressage Absolu Long:MOVE.B $10000, D0 Le contenu de la case $10000 (32 bits) est mis dans D0

Adressage Indirect:MOVE.B (A0), D0 Le contenu de la case mémoire dont l'adresse se trouve dans A0 est mis dans D0

Adressage Indirect avec Post Incrémentation:MOVE.B D0, (A1)+ Le contenu de D0 est mis dans la case mémoire dont l'adresse se trouve dans A1. Le registre A1 est ensuite incrémenté

Adressage Indirect avec Pré Décrémentation:MOVE.B -(A1), D0 Le registre A1 est décrémenté‚ et le contenu de la case mémoire dont l'adresse se trouve dans A1 est mis dans D0

Adressage Indirect avec Déplacement:MOVE $02(A0), D1 Le contenu de la case mémoire dont l'adresse est indiquée par A0+$02 est mis dans D1

Adressage Indirect avec Déplacement et Index:MOVE $02(A1, D0.W), A2 Le contenu de la case mémoire dont l'adresse est indiquée par A1+$02+[16 bits poids faible de D0] est mis dans A2

Adressage Relatif au PC:BNE Boucle L'adresse est indiquée par PC + Boucle

Adressage Indexé Relatif au PC:MOVE Label(A1), D0 Le contenu de la case mémoire dont l'adresse est donnée par A1+Label est mis dans D0Jeu d'instructions

-

- ABCD Addition décimale avec le bit d'extension X du CCR

Syntaxe: ABCD Dy, Dx ou ABCD -(Ay),-(Ax) Opérande: Octet Addition BCD entre deux registres de données Dy,Dx ou entre deux cases mémoires adressées en -(Ay),-(Ax). CCR X: Idem à C V: Indéfini N: Indéfini C: 1 si retenue décimale, sinon 0 Z: 0 si résultat<>0, sinon inchangé Exemple: ABCD D0, D1 ABCD -(A0), -(A1)-

- ADD Addition binaire

Syntaxe: ADD <AE>, Dn ou ADD Dn, <AE> Opérande: Octet, Mot, Mot long Addition binaire entre un opérande et le contenu d'un registre Dn. CCR X: Idem à C V: 1 si débordement N: 1 si résultat<0 C: 1 si retenue Z: 1 si résultat=0 Exemple: ADD.W #$1234, D0 ADD.L D0, -(A1)-

- ADDA Addition avec registre d'adresse

Syntaxe: ADDA <AE>, An Opérande: Mot, Mot long Addition binaire entre un opérande et le contenu d'un registre An. CCR Non affecté Exemple: ADDA.W #$1234, A0 ADDA.L -(A1), A0-

- ADDI Addition immédiate

Syntaxe: ADDI #<donnée>, <AE> Opérande: Octet, Mot, Mot long Addition binaire entre la donnée immédiate et l'opérande de destination. CCR X: Idem à C V: 1 si débordement N: 1 si résultat<0 C: 1 si retenue Z: 1 si résultat=0 Exemple: ADDI.W #$1234, D0 ADDI.B #$03, (A1)+-

- ADDQ Addition rapide

Syntaxe: ADDQ #<donnée>, <AE> Opérande: Octet, Mot, Mot long Addition binaire entre la donnée immédiate et l'Opérande de destination. La donnée est comprise entre $01 et $08. CCR X: Idem à C V: 1 si débordement N: 1 si résultat<0 C: 1 si retenue Z: 1 si résultat=0 Exemple: ADDQ.B #$01, D0 ADDQ.L #$07, $02(A1)-

- ADDX Addition binaire avec le bit d'extension

Syntaxe: ADDX Dy, Dx ou ADDX -(Ay), -(Ax) Opérande: Octet, Mot, Mot long Addition de la source et de la destination avec le bit d'extension X du CCR. CCR X: Idem à C V: 1 si débordement N: 1 si résultat<0 C: 1 si retenue Z: 0 si résultat<>0 sinon inchang‚ Exemple: ADDX.B D0, D1 ADDX.L -(A0), -(A1)-

- AND ET logique

Syntaxe: AND <AE>, Dn ou AND Dn, <AE> Opérande: Octet, Mot, Mot long ET logique entre source et destination. CCR X: Non affecté V = 0 N: 1 si le MSB du résultat=1 C = 0 Z: 1 si résultat=0 Exemple: AND.W #$1234, D0 AND.L -(A2), D3-

- ANDI ET logique immédiat

Syntaxe: ANDI #<donnée>, <AE> Opérande: Octet, Mot, Mot long ET logique entre la donnée immédiate et la destination. CCR X: Non affecté V = 0 N: 1 si le MSB du résultat=1 C = 0 Z: 1 si résultat=0 Exemple: ANDI.W #$1234, D0 ANDI.B #$03, -(A2)-

- ANDI to CCR

Syntaxe: ANDI #<donnée 8 bits>, CCR Opérande: Octet ET logique entre une donnée 8 bits et le CCR CCR X, N, Z, V, C: Résultat de l'opération CCR And #<donnée> Exemple: ANDI.B #$12, CCR-

- ANDI to SR

Syntaxe: ANDI #<donnée 16 bits>, SR Opérande: Mot ET logique entre une donnée 16 bits et le SR. Le processeur doit être en mode Superviseur. CCR X, N, Z, V, C: Résultat de l'opération SR And #<donnée b4..b0> Exemple: ANDI.L #$1234, SR-

- ASL décalage arithmétique gauche

Syntaxe: ASL Dx, Dy ou ASL #<donnée>, Dy ou ASL <AE> Opérande: Octet, Mot, Mot long décalage arithmétique gauche des bits de l'Opérande. Registre: Nombre de décalages -> donnée immédiate (0-7) Stocké dans Dx Case mémoire: Un seul décalage, exclusivement sur un mot. CCR X: Idem C V: 1 si le MSB a été modifié N: 1 si le MSB du résultat=1 C: Dernier bit sorti de l'Opérande Z: 1 si résultat=0 Exemple: ASL.B D0, D1 ASL.W #$1234, D0 ASL (A1)+-

- ASR décalage arithmétique droit

Syntaxe: ASR Dx, Dy ou ASR #<donnée>, Dy ou ASR <AE> Opérande: Octet, Mot, Mot long décalage arithmétique droit des bits de l'Opérande. Registre: Nombre de décalages -> donnée immédiate (0-7) Stocké dans Dx Case mémoire: Un seul décalage, exclusivement sur un mot. CCR X: Idem C V: 1 si le MSB a été modifié N: 1 si le MSB du résultat=1 C: Dernier bit sorti de l'Opérande Z: 1 si résultat=0 Exemple: ASR.B D0, D1 ASR.W #$1234, D0 ASR (A1)+-

- BCC à BVS Branchements conditionnels

Syntaxe, par exemple: BEQ <étiquette> Les branchements, ou sauts, sont effectués en fonction du contenu du CCR. Si la condition est vraie, l'exécution du programme se poursuit à l'adresse (PC) + déplacement mentionné par l' étiquette. Exemple: BEQ $06 BNE LaBas CCR Non affecté Description: Conditions CCR BCC: Branchement si retenue à zéro C=0 BCS: Branchement si retenue à un C=1 BEQ: Branchement si égal Z=1 BNE: Branchement si différent Z=0 BGE: Branchement si supérieur ou égal N xor V = 0 BGT: Branchement si supérieur Z + [N xor V] = 0 BHI: Branchement si supérieur C + Z = 0 BLE: Branchement si inférieur ouégal Z + [N xor V] = 1 BLS: Branchement si inférieur ou égal C + Z = 1 BLT: Branchement si inférieur N xor V = 1 BMI: Branchement si négatif N=1 BPL: Branchement si positif N=0 BVC: Branchement si pas de dépassement V=0 BVS: Branchement si dépassement V=1 BT: Branchement si vrai tout le temps BF: Branchement si faux jamais-

- BCHG Test d'un bit et modification

Syntaxe: BCHG Dn, <AE> ou BCHG #<donnée>, <AE> Opérande: Octet, Mot long Un bit de la destination est testé pour permettre le positionnement du flag Z du CCR, puis le bit est inversé. Dans le cas d'une opération sur une case mémoire, les bits 0 à 7 peuvent être testés (octet). CCR X: Non affecté V: Non affecté N: Non affecté C: Non affecté Z: 1 si résultat=0 Exemple: BCHG.L D0, D1 BCHG.B #$02, -(A1)-

- BCLR Test d'un bit et remise à zéro

Syntaxe: BCLR Dn, <AE> ou BCLR #<donnée>, <AE> Opérande: Octet, Mot long Un bit de la destination est testé pour permettre le positionnement du flag Z, puis ce bit est mis à zéro. Dans le cas d'une opération sur une case mémoire, les bits 0 à 7 peuvent être testés (octet). CCR X: Non affecté V: Non affecté N: Non affecté C: Non affecté Z: 1 si résultat=0 Exemple: BCLR.L D0, D1 BCLR.B #$02, -(A1)-

- BRA Branchement inconditionnel

Syntaxe: BRA <étiquette> Opérande: Octet, Mot L'instruction suivante qui sera exécutée est située à l'adresse (PC) + étiquette CCR Non affecté Exemple: BRA $02 BRA LàBas-

- BSET Test d'un bit et mise à un

Syntaxe: BSET Dn, <AE> ou BSET #<donnée>, <AE> Opérande: Octet, Mot long Un bit de la destination est testé pour permettre le positionnement du flag Z, puis ce bit est mis à un. Dans le cas d'une opération sur une case mémoire, les bits 0 à 7 peuvent être testés (octet). CCR X: Non affecté V: Non affecté N: Non affecté C: Non affecté Z: 1 si résultat=0 Exemple: BSET.L D0, D1 BSET.B #$02, -(A1)-

- BSR Branchement sous-programme

Syntaxe: BSR <étiquette> Opérande: Octet, Mot L'adresse de l'instruction suivante est sauvegardée dans la pile puis l'exécution du programme se poursuit à l'adresse (PC) + étiquette CCR Non affecté Exemple: BSR $02 BSR LàBas-

- BTST Test d'un bit

Syntaxe: BTST Dn, <AE> ou BTST #<donnée>, <AE> Opérande: Octet, Mot long Un bit de la destination est testé pour permettre le positionnement du flag Z. Le bit testé n'est pas modifié. Dans le cas d'une opération sur une case mémoire les bits 0 à 7 peuvent être testés (octet). CCR X: Non affecté V: Non affecté N: Non affecté C: Non affecté Z: 1 si résultat=0 Exemple: BTST.L D0, D1 BTST.B #$02, -(A1)-

- CHK Test des limites d'un registre

Syntaxe: CHK <AE>, Dn Opérande: Mot Les 16 bits de poids faible du registre de données Dn sont comparés ainsi: Si (Dn) < 0 ou (Dn) > (<AE>), le processeur génère l'exception Chk. CCR X: Non affecté V: indéfini N: 1 si (Dn)<0, 0 si (Dn)>(<AE>) C: indéfini Z: indéfini Exemple: CHK.W D0, D1 CHK.W -(A1), D2 CHK.W #$1234, D2-

- CLR Remise à zéro d'un Opérande

Syntaxe: CLR <AE> Opérande: Octet, Mot, Mot long Tous les bits de la destination sont mis à zéro. CCR X: Non affecté V: =0 N: =0 C: =0 Z: =1 Exemple: CLR.L D1 CLR.B -(A1)-

- CMP Comparaison Registre Dn

Syntaxe: CMP <AE>, Dn Opérande: Octet, Mot, Mot long L'Opérande source est soustrait de l'Opérande destination afin de positionner les flags CCR. CCR X: Non affecté V: 1 si débordement N: 1 si résultat<0 C: 1 si retenue Z: 1 si résultat=0 Exemple: CMP.L D0, D1 CMP.W #$1234, D2 CMP.L -(A1), D0-

- CMPA Comparaison Adresse An

Syntaxe: CMPA <AE>, An Opérande: Mot, Mot long L'Opérande source est soustrait de l'Opérande destination afin de positionner les flags CCR. CCR X: Non affecté V: 1 si débordement N: 1 si résultat<0 C: 1 si retenue Z: 1 si résultat=0 Exemple: CMP.L D0, A1 CMP.W #$1234, A2 CMP.L -(A1), A0-

- CMPI Comparaison immédiate

Syntaxe: CMPI #<donnée>, <AE> Opérande: Octet, Mot, Mot long La donnée immédiate est soustraite de l'Opérande destination afin de positionner les flags CCR. CCR X: Non affecté V: 1 si débordement N: 1 si résultat<0 C: 1 si retenue Z: 1 si résultat=0 Exemple: CMPI.B #$02, D1 CMPI.W #$1234, (A1)+ CMPI.L #$12345678, -(A3)-

- CMPM Comparaison mémoire

Syntaxe: CMPM (Ay)+, (Ax)+ Opérande: Octet, Mot, Mot long L'Opérande source est soustrait de l'Opérande destination afin de positionner les flags CCR. CCR X: Non affecté V: 1 si débordement N: 1 si résultat<0 C: 1 si retenue Z: 1 si résultat=0 Exemple: CMPA.L (A1)+, (A0)+ CMPA.B (A2)+, (A1)+-

- DBCC .. DBVS

Test condition, décrémentation et branchement. Syntaxe: DBcc Dn, <étiquette> Opérande: Mot CCR: Non affecté - Si la condition est vérifiée (Dn=-1): Pas d'opération. - Si la condition n'est pas vérifiée (Dn<>-1): - Dn=Dn-1 - Branchement à l'adresse (PC) + déplacement mentionné par l' étiquette. Les conditions sont celles des instructions BCC..BVS. Exemple: DBNE D0, $02 DBEQ D1, LaBas-

- DIVS Division signée

Syntaxe: DIVS <AE>, Dn Opérande: Mot Division de l'Opérande destination 32 bits par l'Opérande source 16 bits. Le résultat 32 bits sign‚ est organis‚ comme suit: - Quotient : Mot de poids faible - Reste : Mot de poids fort. Le signe du reste est le mˆme que celui du dividende, le débordement peut être positionn‚. CCR X: Non affecté V: 1 si débordement N: 1 si quotient<0, indéfini si V=1 C: =0 Z: 1 si quotient=0, indéfini si V=1 Exemple: DIVS.W #$1234, D0 DIVS.W -(A1), D2-

- DIVU Division non signée

Syntaxe: DIVU <AE>, Dn Opérande: Mot Division de l'Opérande destination 32 bits par l'Opérande source 16 bits. Le résultat 32 bits non sign‚ est organis‚ comme suit: - Quotient : Mot de poids faible - Reste : Mot de poids fort. CCR X: Non affecté V: 1 si débordement N: 1 si MSB quotient=1, indéfini si V=1 C: =0 Z: 1 si quotient=0, indéfini si V=1 Exemple: DIVU.W #$1234, D0 DIVU.W -(A1), D2-

- EOR OU Exclusif XOR

Syntaxe: EOR Dn, <AE> Opérande: Octet, Mot, Mot long OU Exclusif XOR entre source et destination, le résultat est mis dans la destination. CCR X: Non affecté V: =0 N: 1 si MSB résultat=1 C: =0 Z: 1 si résultat=0 Exemple: EOR.W D0, D1 EOR.B D1, $12345678 EOR.L D2, (A1)+ Voir aussi EORI.-

- EORI OU Exclusif XOR immédiat

Syntaxe: EORI #<donnée>, <AE> Opérande: Octet, Mot, Mot long OU Exclusif XOR entre donnée immédiate et destination, le résultat est mis dans la destination. CCR X: Non affecté V: =0 N: 1 si MSB résultat=1 C: =0 Z: 1 si résultat=0 Exemple: EORI.W #$1234, (A1)+ EORI.B #$12, $12345678 Voir aussi EORI to CCR, EORI to SR.-

- EORI to CCR

Syntaxe: EORI #<donnée 8 bits>, CCR Opérande: Octet OU Exclusif XOR entre les 8 bits de la donnée immédiate et le registre CCR CCR X, N, Z, V, C: Résultat de l'opération CCR XOR #<donnée> Exemple: EORI.B #$12, CCR Voir aussi EORI to SR.-

- EORI to SR

Syntaxe: EORI #<donnée 16 bits>, SR Opérande: Mot OU Exclusif XOR entre les 16 bits de la donnée immédiate et le registre d'état SR si le processeur est en mode Superviseur. CCR X, N, Z, V, C: (Recopie dans CCR du résultat de l'opération SR XOR #<donnée>) Exemple: EORI.W #$1234, SR-

- EXG Echange de registres

Syntaxe: EXG Rx, Ry Opérande: Mot long Echange entre deux registres 32 bits. Ces ‚changes peuvent être: - Dn, An, Dn-An, An-Dn. CCR Non affecté Exemple: EXG D1, A2-

- EXT Extension du signe d'un registre de données

Syntaxe: EXT Dn Opérande: Mot, Mot long Sur un Mot: Recopie du bit 7 sur les bits 8 à 15. Sur un Mot long: Recopie du bit 15 sur les bits 16 à 31. CCR X: Non affecté V: =0 N: 1 si résultat<0 C: =0 Z: 1 si résultat=0 Exemple: EXT.W D1-

- ILLEGAL

Cette instruction génère l'exception "Instruction Illégale" de vecteur nø4. CCR Non affecté-

- JMP Saut de type Jump

Syntaxe: JMP <AE> Opérande: Aucun L'excution se poursuit à l'adresse spécifié dans l'instruction, qui peut être une étiquette. CCR: Non affecté Exemple: JMP.L (A1) JMP LàBas-

- JSR Saut vers un sous programme

Syntaxe: JSR <AE> Opérande: Aucun L'exécution se poursuit à l'adresse spécifié dans l'instruction, qui peut être une étiquette. L'adresse de l'instruction suivante est d'abord mise sur la pile. CCR: Non affecté Exemple: JSR.L (A1) JSR LaBas-

- LEA Chargement adresse effective

Syntaxe: LEA <AE>, An Opérande: Mot long Les 32 bits de l'adresse effective sont chargés dans le registre d'adresse An. CCR Non affecté Exemple: LEA.L $12345678, A1 LEA.L $04(A0), A2-

- LINK Réalisation de liens Link

Syntaxe: LINK An, #<déplacement 16 bits> Opérande: Aucun Le contenu de An est mis sur la pile, puis An est chargé avec la valeur du SP. Enfin, le déplacement immédiat est ajouté au SP avec extension sur 32 bits. CCR: Non affecté Exemple: LINK A1, #$1234

-

- LSL décalage logique gauche

Syntaxe: LSL Dx, Dy ou LSL #<donnée>, Dy ou LSL <AE> Opérande: Octet, Mot, Mot long décalage logique gauche des bits de l'Opérande. Registre: Nombre de décalages -> donnée immédiate (0-7) Stock‚ dans Dx Case mémoire: Un seul décalage, exclusivement sur un mot. CCR X: Idem C V: =0 N: 1 si résultat<0 C: Dernier bit sorti de l'Opérande Z: 1 si résultat=0 Exemple: LSL.B D0, D1 LSL.W #$1234, D0 LSL (A1)+-

- LSR décalage logique droit

Syntaxe: LSR Dx, Dy ou LSR #<donnée>, Dy ou LSR <AE> Opérande: Octet, Mot, Mot long décalage logique droit des bits de l'Opérande. Registre: Nombre de décalages -> donnée immédiate (0-7) Stock‚ dans Dx Case mémoire: Un seul décalage, exclusivement sur un mot. CCR X: Idem C V: =0 N: 1 si résultat<0 C: Dernier bit sorti de l'Opérande Z: 1 si résultat=0 Exemple: LSR.B D0, D1 LSR.W #$1234, D0 LSR (A1)+-

- MOVE Transfert de données

Syntaxe: MOVE <AE>, <AE> Opérande: Octet, Mot, Mot long Transfert de l'Opérande Source vers la Destination CCR X: Non affecté V: =0 N: 1 si résultat < 0 C: =0 Z: 1 si résultat = 0 Exemple: MOVE.W D0, D1 MOVE.B D1, $12345678 MOVE.L D2, (A1)+-

- MOVE to CCR Transfert vers le CCR

Syntaxe: MOVE <AE>, CCR Opérande: Mot Transfert de l'Opérande Source vers le CCR. Remarque: Seuls les 8 bits de poids faible sont pris en compte CCR X: Bit 4 de la source V: Bit 1 de la source N: Bit 3 de la source C: Bit 0 de la source Z: Bit 2 de la source Exemple: MOVE.W D0, CCR MOVE.W #$1234, CCR MOVE -(A0), CCR-

- MOVEA Transfert vers un registre d'adresse

Syntaxe: MOVE <AE>, An Opérande: Mot, Mot long Transfert de l'Opérande Source vers un registre d'adresse. Un Opérande source 16 bits voit son signe étendu à 32 bits. CCR X: Non affecté V: Non affecté N: Non affecté C: Non affecté Z: Non affecté Exemple: MOVEA.W $02(A1), A0 MOVEA.L #$12345678, A1-

- MOVE USP Transfert le pointeur de pile utilisateur USP

Syntaxe: MOVE USP, An ou MOVE An, USP Opérande: Mot long Le contenu du pointeur de pile utilisateur USP est transféré de ou vers le registre d'adresse An. CCR X: Non affecté V: Non affecté N: Non affecté C: Non affecté Z: Non affecté Exemple: MOVE USP, A1 MOVE A0, USP-

- MOVE From SR Transfert depuis SR

Syntaxe: MOVE SR, <AE> Opérande: Mot Le contenu du registre d'état est transféré à l'emplacement Destination CCR X: Non affecté V: Non affecté N: Non affecté C: Non affecté Z: Non affecté Exemple: MOVE SR, D0 MOVE SR, $02(A1)-

- MOVE To SR Transfert vers le SR

Syntaxe: MOVE <AE>, SR Opérande: Mot L'Opérande Source est transféré dans le registre d'état SR. On doit être en mode Superviseur, sinon "violation de privilège" CCR X: Non affecté V: Non affecté N: Non affecté C: Non affecté Z: Non affecté Exemple: MOVE D0, SR MOVE $02(A1), SR-

- MOVEQ Transfert rapide

Syntaxe: MOVEQ #<donnée>, Dn Opérande: Mot long Transfert d'une donnée immédiate dans un registre de données. La données est de 8 bits et sera ‚tendue à 32 bits. CCR X: Non affecté V: =0 N: 1 si résultat < 0 C: =0 Z: 1 si résultat = 0 Exemple: MOVEQ #$12, D0-

- MULS Multiplication signée

Syntaxe: MULS <AE>, Dn Opérande: Mot Multiplication 2 x 16 bits, résultat sign‚ sur 32 bits dans Dn CCR X: Non affecté V: =0 N: 1 si résultat < 0 C: =0 Z: 1 si résultat = 0 Exemple: MULS D0, D1 MULS #$1234, D2 MULS $1234, D3-

- MULU Multiplication non signée

Syntaxe: MULU <AE>, Dn Opérande: Mot Multiplication 2 x 16 bits, résultat non sign‚ sur 32 bits dans Dn CCR X: Non affecté V: =0 N: 1 si MSB résultat=1 C: =0 Z: 1 si résultat = 0 Exemple: MULU D0, D1 MULU #$1234, D2 MULU $1234, D3-

- NBCD Complémentation décimale avec le bit d'extension

Syntaxe: NBCD <AE> Opérande: Octet L'Opérande et le bit X du CCR sont soustraits à zéro, le résultat est mis dans l'Opérande. Si X=0, on a un complément à 10, sinon il s'agit d'une complémentation à 9. CCR X: =1 si retenue décimale V: indéfini N: indéfini C: =1 si retenue décimale Z: 0 si résultat <> 0 Exemple: NBCD D0 NBCD $1234-

- NEG Négation

Syntaxe: NEG <AE> Opérande: Octet, Mot, Mot long L'Opérande est soustrait de zéro. Le résultat est remis dans l'Opérande. CCR X: =1 si retenue décimale V: =1 si débordement N: =1 si résultat < 0 C: =1 si retenue décimale Z: =1 si résultat = 0 Exemple: NEG.W D0 NEG.L $02(A0)-

- NEGX Négation avec le bit d'extension

Syntaxe: NEGX <AE> Opérande: Octet, Mot, Mot long L'Opérande et le bit X sont soustraits de zéro. Le résultat est remis dans l'Opérande. CCR X: =1 si retenue décimale V: indéfini N: indéfini C: =1 si retenue décimale Z: =0 si résultat <> 0 Exemple: NEGX.W D0 NEGX.L $02(A0)-

- NOP Pas d'opération

Syntaxe: NOP Opérande: Aucun Aucune opération ne se produit, l'état du processeur reste inchangé, sauf pour le PC qui pointe sur l'instruction suivante. CCR X: Non affecté V: Non affecté N: Non affecté C: Non affecté Z: Non affecté Exemple: NOP-

- NOT Compl‚ment à un

Syntaxe: NOT <AE> Opérande: Octet, Mot, Mot long Complément à un de l'Opérande. CCR X: Non affecté V: =0 N: =1 si résultat < 0 C: =0 Z: =1 si résultat = 0 Exemple: NOT.W D0 NOT.L $02(A0)-

- OR OU logique inclusif

Syntaxe: OR <AE>, Dn ou OR Dn, <AE> Opérande: Octet, Mot, Mot double OU logique entre la source et la destination. CCR X: Non affecté V: =0 N: =1 si MSB résultat=1 C: =0 Z: =1 si résultat = 0 Exemple: OR.W D1, D0 OR.L D1, $02(A3)-

- ORI OU logique inclusif immédiat

Syntaxe: ORI #<donnée>, <AE> Opérande: Octet, Mot, Mot double OU logique entre la donnée immédiate et la destination. CCR X: Non affecté V: =0 N: =1 si MSB résultat=1 C: =0 Z: =1 si résultat = 0 Exemple: ORI.B #$03, (A1)+ ORI.W #$1234, D1-

- ORI to CCR OU logique inclusif avec le CCR

Syntaxe: ORI #<donnée>, CCR Opérande: Octet OU logique entre la donnée immédiate 8 bits et le CCR. CCR X: =1 si bit 4 donnée =1 V: =1 si bit 1 donnée =1 N: =1 si bit 3 donnée =1 C: =1 si bit 0 donnée =1 Z: =1 si bit 2 donnée =1 Exemple: ORI #$02, CCR-

- ORI to SR OU logiqueinclusif avec le SR

Syntaxe: ORI #<donnée 16 bits>, SR Opérande: Octet OU logique entre la donnée immédiate 16 bits et le SR. Le processeur doit être en mode Superviseur, sinon "violation de indiqué". CCR X: =1 si bit 4 donnée =1 V: =1 si bit 1 donnée =1 N: =1 si bit 3 donnée =1 C: =1 si bit 0 donnée =1 Z: =1 si bit 2 donnée =1 Exemple: ORI #$0002, SR Registre SR-

- PEA Sauvegarde adresse effective

Syntaxe: PEA <AE> Opérande: Mot long L'adresse effective est mise sur la pile. CCR X: Non affecté V: Non affecté N: Non affecté C: Non affecté Z: Non affecté Exemple: PEA (A0) PEA $1234-

- RESET Remise à zéro des circuits externes

Syntaxe: RESET Opérande: Aucun La sortie Hardware Reset est validée si on est en mode superviseur. Sinon, violation de provolège indiqué. CCR X: Non affecté V: Non affecté N: Non affecté C: Non affecté Z: Non affecté Exemple: RESET-

- ROL Rotation à gauche

Syntaxe: ROL Dx, Dy ou ROL #<donnée>, Dy ou ROL <AE> Opérande: Octet, Mot, Mot long Rotation à gauche de la destination. Le nombre de rotations est indiqué par la source. Si l'Opérande est une case mémoire, il n'y a qu'une rotation. La rotation de 0 bit est parfois interdite par les compilateurs. Lorsqu'elle est autorisée, elle correspond en fait à une rotation de 8 bits. CCR X: Non affecté V: =0 N: =1 si MSB résultat =1 C: dernier bit hors de l'Opérande Z: =1 si résultat =0 ou 0 pour une rotation nulle. Exemple: ROL (A0)+ ROL #$01, D0-

- ROR Rotation à droite

Syntaxe: ROR Dx, Dy ou ROR #<donnée>, Dy ou ROR <AE> Opérande: Octet, Mot, Mot long Rotation à droite de la destination. Le nombre de rotations est indiqué par la source. Si l'Opérande est une case mémoire, il n'y a qu'une rotation. La rotation de 0 bit est parfois interdite par les compilateurs. Lorsqu'elle est autorisée, elle correspond en fait à une rotation de 8 bits. CCR X: Non affecté V: =0 N: =1 si MSB résultat =1 C: dernier bit hors de l'Opérande Z: =1 si résultat =0 ou 0 pour une rotation nulle. Exemple: ROR (A0)+ ROR #$01, D0-

- ROLX Rotation à gauche avec le bit d'extension

Syntaxe: ROLX Dx, Dy ou ROLX #<donnée>, Dy ou ROLX <AE> Opérande: Octet, Mot, Mot long Rotation à gauche de la destination. Le nombre de rotations est indiqué par la source. La rotation se fait par le bit X. Si l'Opérande est une case mémoire, il n'y a qu'une rotation. CCR X: Idem C V: =0 N: =1 si MSB résultat =1 C: dernier bit hors de l'Opérande Z: =1 si résultat =0 ou 0 pour une rotation nulle. Exemple: ROLX (A0)+ ROLX #$01, D0-

- RORX Rotation à droite avec le bit d'extension

Syntaxe: RORX Dx, Dy ou RORX #<donnée>, Dy ou RORX <AE> Opérande: Octet, Mot, Mot long Rotation à droite de la destination. Le nombre de rotations est indiqué par la source. La rotation se fait par le bit X. Si l'Opérande est une case mémoire, il n'y a qu'une rotation. CCR X: Idem C V: =0 N: =1 si MSB résultat =1 C: dernier bit hors de l'Opérande Z: =1 si résultat =0 ou 0 pour une rotation nulle. Exemple: RORX (A0)+ RORX #$01, D0-

- RTE Retour d'exception

Syntaxe: RTE Opérande: Aucun Le registre SR et le PC sont restitués par la pile si le processeur est en mode superviseur, sinon "violation de privilège". CCR X: Suivant mot dépilé V: Suivant mot dépilé N: Suivant mot dépilé C: Suivant mot dépilé Z: Suivant mot dépilé Exemple: RTE-

- RTR Retour et restitution des Codes Condition

Syntaxe: RTR Opérande: Aucun Le registre CCR et le PC sont restitués par la pile. Le registre SR n'est pas affecté. CCR X: Suivant mot dépilé V: Suivant mot dépilé N: Suivant mot dépilé C: Suivant mot dépilé Z: Suivant mot dépilé Exemple: RTR-

- RTS Retour de sous-programme

Syntaxe: RTS Opérande: Aucun Le registre PC est restitué par la pile. CCR X: Non affecté V: Non affecté N: Non affecté C: Non affecté Z: Non affecté Exemple: RTS-

- SBCD Soustraction décimale avec le bit d'extension

Syntaxe: SBCD Dy, Dx ou SBCD -(Ay), -(Ax) Opérande: Octet Soustraction de la Source et du bit X à la Destination. Le résultat en décimal codé binaire est mis dans la Destination. CCR X: =1 si retenue décimale V: indéfini N: indéfini C: =1 si retenue décimale Z: =0 si résultat <> 0 Exemple: SBCD D0, D1 SBCD -(A1), -(A0)-

- Scc Positionnement selon condition

Syntaxe: Scc <AE> Opérande: Octet La condition spécifié est testée. Si la condition est vraie, l'octet adressé par <AE> est mis à $FF. Sinon, il est mis à $00. CCR X: Non affecté V: Non affecté N: Non affecté C: Non affecté Z: Non affecté Exemple: SEQ Etiquette SNE LaBas-

- STOP Chargement du SR et arrêt

Syntaxe: STOP #<donnée 16 bits> Opérande: Aucun La donnée immédiate 16 bits est mise dans le SR. Le PC est positionné sur la prochaine instruction et le processeur s'arrête. L'exécution reprend après une exception Trace, une interruption ou un Reset. Le processeur doit être en mode Superviseur. CCR X: Suivant donnée immédiate V: Suivant donnée immédiate N: Suivant donnée immédiate C: Suivant donnée immédiate Z: Suivant donnée immédiate Exemple: STOP #$1234-

- SUB Soustraction binaire

Syntaxe: SUB <AE>, Dn ou SUB Dn, <AE> Opérande: Octet, Mot, Mot long Soustraction de la Source et de la Destination. Le résultat est mis dans la Destination. CCR X: =1 si retenue V: =1 si débordement N: =1 si résultat < 0 C: =1 si retenue Z: =1 si résultat = 0 Exemple: SUB.W D0, D1 SUB.W $02(A1), D0-

- SUBA Soustraction à un registre d'adresse

Syntaxe: SUBA <AE>, An Opérande: Mot, Mot long Soustraction de la Source et de la Destination. Le résultat est mis dans la Destination et l'Opérande source est étendu à 32 bits avant l'opération. CCR X: Non affecté V: Non affecté N: Non affecté C: Non affecté Z: Non affecté Exemple: SUBA.W D0, A1 SUBA.L $02(A1), A0-

- SUBI Soustraction immédiate

Syntaxe: SUBI #<donnée>, <AE> Opérande: Octet, Mot, Mot long Soustraction de la donnée immédiate et de la Destination. Le résultat est mis dans la Destination. CCR X: =1 si retenue V: =1 si débordement N: =1 si résultat < 0 C: =1 si retenue Z: =1 si résultat = 0 Exemple: SUBI.W #$1234, D1 SUBI.B #$12, (A1)+-

- SUBQ Soustraction rapide

Syntaxe: SUBQ #<donnée 8 bits>, <AE> Opérande: Octet, Mot, Mot long Soustraction de la donnée immédiate et de la Destination. La donnée peut prendre les valeurs 1 à 8. Le résultat est mis dans la Destination. Le CCR n'est pas affecté dans le cas de la soustraction à un registre d'adresse. CCR X: =1 si retenue V: =1 si débordement N: =1 si résultat < 0 C: =1 si retenue Z: =1 si résultat = 0 Exemple: SUBQ.B #$01, D0 SUBQ.L #$01, $02(A1)-

- SUBX Soustraction avec bit d'extension

Syntaxe: SUBX Dy, Dx ou SUBX -(Ay), -(Ax) Opérande: Octet, Mot, Mot long Soustraction de la Source et du bit X à la Destination. Le résultat est mis dans la Destination. CCR X: =1 si retenue V: =1 si débordement N: =1 si résultat < 0 C: =1 si retenue Z: =0 si résultat <> 0 Exemple: SUBX.B D0, D1 SUBX.L -(A1), -(A0)-

- SWAP Echange interne

Syntaxe: SWAP Dn Opérande: Mot Echange entre les 16 bits de poids faible et les 16 bits de poids fort d'un registre de données. CCR X: Non affecté V: =0 N: =1 MSB résultat = 1 C: =0 Z: =1 si résultat = 0 Exemple: SWAP D3-

- TAS Test d'un octet et mise à 1 du bit 7

Syntaxe: TAS <AE> Opérande: Octet Test d'un octet par l'adresse effective dont le bit 7 est mis à 1. CCR X: Non affecté V: =0 N: =1 MSB résultat = 1 C: =0 Z: =1 si résultat = 0 Exemple: TAS D0 TAS $02(A1)-

- TRAP Demande d'exception Trap

Syntaxe: TRAP #<numéro> Opérande: Aucun Le processeur entame une procédure d'exception. Le numéro permet de disposer de 16 vecteurs propres à l'instruction TRAP. CCR X: Non affecté V: Non affecté N: Non affecté C: Non affecté Z: Non affecté Exemple: TRAP #1-

- TRAPV Exception si débordement

Syntaxe: TRAPV Opérande: Aucun Si le bit V du CCR est positionn‚, il y a génération de l'exception de vecteur nø 7. Sinon, l'exécution du programme se poursuit normalement. CCR X: Non affecté V: Non affecté N: Non affecté C: Non affecté Z: Non affecté Exemple: TRAPV-

- TST Test d'un Opérande

Syntaxe: TST <AE> Opérande: Octet, Mot, Mot long L'Opérande est comparé à zéro. Les codes condition sont alors positionnés. CCR X: Non affecté V: =0 N: =1 si résultat < 0 C: =0 Z: =1 si résultat = 0 Exemple: TST.W D0 TST.L $02(A1)-

- UNLK Déconnexion (UnLink)

Syntaxe: UNLK An Opérande: Aucun Le registre d'adresse An est transféré dans le pointeur de pile. Le contenu de la pile est ensuite transféré dans An. Il s'agit du processus complémentaire de LINK. CCR X: Non affecté V: Non affecté N: Non affecté C: Non affecté Z: Non affecté Exemple: UNLK A2Utilisations du 68000

Par Airbus

Pour le calcul des lois de pilotage de l'A320, au sein des ELAC (Elevator and Aileron Computer).

Par Apple

Pour ses ordinateurs personnels, d'abord le Lisa, puis les premiers Macintosh (Macintosh 128K, Mac 512K, Mac Plus, Mac SE et Classic).

Par Atari

Dans sa gamme d'ordinateurs personnels Atari ST ainsi que pour la console Jaguar.

Par Commodore International

Dans sa gamme d'ordinateurs personnels Amiga (Amiga 1000, Amiga 2000, Amiga 500, Amiga 600, CDTV).

Par Epsitec

Pour ses ordinateurs personnels Smaky 8 et 100.

Par Sega

Pour sa console de jeux vidéo Megadrive.

Par Silicon Graphics

Pour ses premiers ordinateurs, prévus pour être utilisés comme terminaux IRIS 1000 et IRIS 1200. …

Par SNK

Pour sa console de jeux vidéo Neo-Geo AES et pour son système d'arcade Neo-Geo MVS.

Par Sun Microsystems

Pour ses premières stations de travail Sun-1 et Sun-100.

Par Texas Instruments

Pour les calculatrices TI-89, TI-89 Titanium, TI-92, TI-92 Plus et TI Voyage 200.

Par Thomson

Pour son micro ordinateur TO16, abandonné au stade final

Lien externe

Liste des microprocesseurs Motorola

CPU 8 bits : 6800 • 6809 • CPU architecture RISC : 88000 CPU architecture 68000 : 68000 • 68008 • 68010 • 68012 • 68020 • 68030 • 68040 • 68060 • DragonBall • ColdFire CPU architecture PowerPC : 601 (G1) • 603 (G2) • PowerPC G3 • PowerPC G4 FPU : 68881/2 • MMU : 68851 DSP : DSP560XX • DSP563XX • DSP566XX • DSP568XX • DSP96XXX - Portail de l’informatique

- Portail de l’électricité et de l’électronique

Catégories : Apple | Microprocesseur 68000 - 8 registres de données 32 bits :

Wikimedia Foundation. 2010.