- Barcelona (informatique)

-

AMD K10

Pour les articles homonymes, voir Agena.

Pour les articles homonymes, voir Agena.K10 est le nom de la neuvième architecture microprocesseur d'AMD. Elle succède au K8. Des rumeurs avaient avancé un nom de code qui aurait pu être K8L ou K9[réf. souhaitée].

La nouvelle architecture est introduite sur le Phenom. Tout ressemble à l'Athlon, mais les flottants sont désormais traités sur 128bits, et la bande passante interne augmente, comme chez Intel. Pas de « memory disambiguation » en revanche. Le bus Hyper Transport augmente sa fréquence.

Sommaire

Nomenclature

AMD abandonne le P-rating (xx00+) pour une nouvelle numérotation. 2 lettres plus 4 chiffres 1ère lettre gamme 2ème lettre dissipation : TDP

1er chiffre famille/architecture : 7 : Phenom 4 cœurs, 6 Phenom bi cœurs, 2 : Athlon X2 , 1 : Athlon mono cœur et Sempron 2ème chiffre et 3ème chiffre puissance en fréquence 4ème chiffre fonctionnalités éventuelles

Historique

Avant qu'AMD publie officiellement ce nom de K10 par les voix de Giuseppe Amato et de Philip G. Eisler (respectivement directeur technique des Ventes et du marketing pour l’Europe et vice-Président de la division chipset d'AMD) en février 2007[1], la presse spécialisée attribuait logiquement le nom K8L à la nouvelle architecture. The Inquirer pensait alors que le "L" se rapportait au chiffre romain signifiant 50, il s'agirait alors du K8.50, soit une version à mi-chemin entre l'architecture K8 et K10. Il apparaît dans l'interview des responsables AMD que le K8L était une dénomination pour des processeurs d'architecture K8 pour PC portable en 65 nm.

Technologies et caractéristiques

Gravure

Les premiers microprocesseurs de la génération K10 seront exclusivement gravés grâce à la technologie de gravure en 65 nm d'AMD en partenariat avec IBM[2] qui utilise des wafers SOI (Silicium sur isolant) 300 mm UNIBOND™ du fabricant français Soitec qui entretient un partenariat privilégié avec AMD[3]. Le partenariat avec IBM permet également à AMD d'utiliser la technologie SiGe d'IBM (ajout de germanium en plus de silicium en vu de rendre les transistors plus performants). Ces microprocesseurs seront sûrement fabriqués dans l'usine Fab 36 d'AMD à Dresde en Allemagne qui fabrique déjà les Athlon 64 en 65 nm[4]. L'usine pourra produire normalement aux alentours de 100 millions de processeurs par an dès 2008 (pour 20 000 wafers)[5] ce qui coïncide avec l'arrivée de l'architecture K10. AMD utilise pour sa gravure en 65 nm ses technologies[6] Continuous Transistor Improvement (CTI) ou amélioration continue de transistor et Shared Transistor Technology (STT) ou partage technologique des transistor ainsi que la technologie Dual Stress Liner (DSL).

Il existera peut-être par la suite des processeurs K10 gravés en 45 voire en 32 nm (Deneb FX, Deneb, Propus, Regor et Sargas), puisqu'AMD compte produire des processeurs grâce à la technologie de lithographie par immersion dès 2008[7].

Mémoire

Les processeurs de la famille K10 tout comme leurs prédécesseurs K8 possèderont leur contrôleur mémoire intégré[8] contrairement aux processeurs Intel qui laissent cette charge au chipset. Cette caractéristique a été en partie responsable du succès des Athlon 64 en réduisant considérablement les latences pour l'accès à la mémoire RAM lorsque la norme était la DDR-SDRAM première du nom. En effet avec ce type de barrettes, les latences de la RAM étaient de 2-2-2-5 pour les meilleures DDR400. Mais lors de l'introduction de la DDR2, l'atout de l'Athlon 64 s'est atténué car les latences ont explosé et l'augmentation de fréquence n'a pu que compenser cette chute de performance. Ainsi les Athlon 64 sur socket AM2 sont juste aussi performant que les Athlon 64 sur socket 939[9]. Les latences mémoires ayant sérieusement diminué, la DDRII ne pose plus de problème. Les K10 seront faits pour supporter de la DDR2 1066MHz en standard. Les serveurs exploiteront la DDR2 800 dans un premier temps.

Les prochaines révisions de cœur de la famille K10 (Deneb FX, Deneb, Propus, Regor et Sargas) prévues pour l'année 2008 voire 2009 seront elles, tournées vers la mémoire DDR3 et le 45 nm qui n'est pas encore sur le marché[10]. Ils seront équipés de 4 ou 6 Mio de cache L3.

Sockets

AMD a fait le choix d'une certaine continuité lors de ce passage au K10. Il n'y aura donc pas comme lors du passage de l'architecture K7 à K8 un changement radical de socket (alors socket A vers socket 754 puis 939 et AM2). AMD a donc nommé le socket de son nouveau processeur AM2+ pour marquer la proximité avec le socket AM2. Le socket AM2+ accueillera donc tous les processeurs K10 à l'exception des processeurs socket 1207 incompatibles. Il s'agit d'un socket de 940 broches. Les différences entre le socket AM2 utilisé actuellement pour les K8 et le socket AM2+ seront la gestion de l'hypertransport 3.0 par ce dernier et la gestion avancée de l'énergie puisque chaque cœur disposera d'une tension propre. Sur socket AM2, les processeurs pourront tout de même varier leur fréquences indépendamment mais pas leur tension. Il y a rétro compatibilité et on pourra profiter de l'architecture K10 sur une carte mère AM2.

Les chipsets pour AM2+ déjà annoncés sont le Nvidia Nforce 7 nom de code MCP72[11], le VIA KT960 et KM960[12] mais aussi les chipsets d'ATI (maintenant propriété d'AMD) RD790+, RD780, RS780, RX780, RS740 et RX740[13].

Les K10 socket AM3 auront probablement deux contrôleurs mémoire, un DDR2 et un DDR3 ainsi ils fonctionneront parfaitement avec une carte mère AM2+. Cependant cette information est à mettre entre pincettes, AMD pourrait très bien changer d'avis car le coût en transistors de deux contrôleurs mémoire pourrait être élevé.

Un K10 AM2+ ne sera pas compatible AM3.

Spécifications

Les caractéristiques complètes des K10 sont celles du premier cœur K10, à savoir le Barcelona. Les versions desktop seront sans doute différentes puisque le Barcelona est fait pour le marché serveur aux demandes particulières.

- Généralités.

- Deux contrôleurs mémoire DDR2 intégrés (Le contrôleur mémoire 128bits des K8 est séparé en deux contrôleurs 64bits pour le K10. Passage prévu à un contrôleur mémoire DDR3).

- Fréquence de fonctionnement entre 1900 et 2 600 MHz (Les versions desktop devraient atteindre les 2 800 MHz).

- 16 niveaux de pipeline.[14]

- Gestion de l'hypertransport 3.0 pour des bus au-delà de 3 GHz (sur socket AM2+, sur socket AM2 la fonction ne sera pas exploitée).

- cache.

- 64 Kio de cache L1 données par cœur (taille identique à celle des K8)

- 64 Kio de cache L1 instructions par cœur (taille identique à celle des K8)

- 512 Kio de cache L2 par cœur (taille identique aux derniers K8. Les Kentsfield offrent 2x4 Mio de cache L2 et le futur Penryn jusqu'à 2×6 Mio).

- 2 Mio de cache L3 partagé.

- Extension possible jusqu'à 8 Mio, 4 à 6 Mio avec le passage au 45 nm: cœur Shangai.

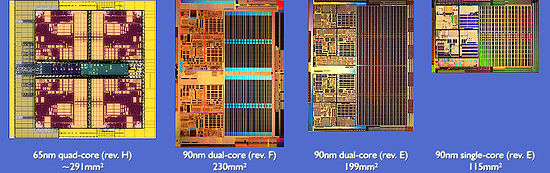

- Le die.

- 1er quadri-cœur dit « natif » produit en masse (Il ne s'agit pas de la juxtaposition de deux circuits bi-cœur comme pour les Core 2 quad Intel.

- Composé de 11 couches de gravure (Contre 9 pour les K8 et 8 pour les core 2 duo. Cela rend le procédé de fabrication un peu plus complexe mais ne change rien pour l'utilisateur. Intel utilisait aussi ce type de procédé avec autant de couches il y a quelques années).

- 463 millions de transistors (Face au 582 millions du Kentsfield mais gravé sur deux die. Ceci s'explique par le fait que le Kentsfield embarque 8,25 Mio de cache alors que le Barcelona se limite à 5,5 Mio).

- 60 millions de transistors non-caches (soit 30%) en plus par rapport au K8.[15]

- améliorations du pipeline et nouvelles Instructions.

- Le SSE 128,

- Gestion d'instruction d'une longueur de 128bits (Contre 64bits pour le K8).

- Gestion parallèle de 32 octets par cycle (Soit le double d'avec le K8. Amélioration qui pourrait bénéficier à d'autres types d'opérations comme par exemple sur les entiers).

- Deux chargements d'instructions par cycle depuis le cache L1 (Nombre stable par rapport au K8 mais donc deux fois plus de données chargées par cycle du fait du passage d'instructions 2*64 à 2*128bits).

- Interface élargie entre le cache L2 et le contrôleur mémoire à 128bits (Pour la cohérence de l'architecture, cad éviter un goulot d'étranglement).

- Introduction des instructions SSE4A.[16]

- Extensions des instructions SSE: EXTRQ/INSERTQ et MOVNTSD/MOVNTSS.

- Apparition des instructions LZCNT et POPCNT utilisées en cryptographie.

- Diminution de la latence sur les divisions d'entiers (ALU) (Les conséquences pratiques devraient être minimes)

- 4 FPU (Floating Point Unit, unités de calcul à virgule flottante) (au lieu de 2 pour le K8. AMD parle d'une amélioration théorique de +300% des performances face au bi-cœur K8 (deux fois plus de cœurs avec deux fois plus de FPU, donc performances quadruplées), mais finalement en pratique l'amélioration serait de l'ordre de 50% face à la concurrence).

- Fastpath.

- Les microinstructions CALL and RET-Imm sont maintenant des instructions qui utilisent Fastpath (elles ne sont plus microcodées).[17]

- Les déplacements entre registres des entiers et registres SSE des instructions MOVs utilisent aussi le Fastpath.

- Le SSE 128,

- Sous-système mémoire, cache et prefetch.

- Diminution de la latence au niveau du cache.

- Meilleure gestion de données Out-Of-Order.[18]

- Prédictions,

- Apparition d'un prédicateur de branchement indirect: 512-entry indirect predictor (Intel avait ajouté ce type de prédicateur sur ses PIV Prescott qui pâtissaient de leur long pipeline et toute erreur de branchement représentait une perte de temps considérable).

- L'espace dédié à la "pile de retour" (return stack) est multiplié par deux.[19]

- La prédiction directe est aussi améliorée par l'augmentation des données "historiques" (Possibilité offerte par la taille gagnée avec le passage au 65 nm alors que l'architecture K8 se contentait au départ du 130 nm).

- Sideband Stack Optimizer équivalent au Dedicated Stack Manager d'Intel.[20]

- TLB (Translation Lookaside Buffer)[21]

- Extension.

- Adressage physique 48bits permettant la gestion de mémoire jusqu'à 256 Tio

- Prefetch:

- 2 prefetch par cœur, un pour les données et un pour les instructions (AMD conserve le nombre de prefetch du K8. À noter que les C2D d'Intel en possèdent trois par cœur).

- Le prefetch charge dans le cache L1 (Le prefetch chargeait dans le cache L2 chez les K8).

- Apparition d'un prefetch de RAM utilisant son propre cache.[22]

- Virtualisation.

- Virtualisation de la mémoire Nested Paging[23]

- Énergie.

- Le voltage du northbridge est maintenant indépendant et s'échelonne de 0.8V à 1.4V.

- Apparition du DICE ou Dynamic Independent Core Engagement ou gestion materielle du PowerNow! permettant la gestion indépendante de la fréquence de chaque cœur.

- TDP compris entre 95W et 120W (TDP entre 45W et 89W pour les Phenom, TDP inconnu pour les Phenom FX)

- Registres

- ajouts de 8 registres supplémentaire pour le 64bits.

Performances

Lors d'une démonstration le 30 novembre 2006[24],[25], AMD annonce et montre à la presse que le Barcelona sera globalement 40% plus performant qu'un Xeon 5355 (quad-core à 2,66 GHz). Dernièrement AMD affirme que son processeur devrait devancer les performances des Xeon quadri-cœurs de 50% sur les calculs en virgule flottante et de 20% sur des calculs liés à des nombres entiers[26]. Cela dit, il est bon de préciser qu’une telle comparaison ne peut pas encore être vérifiée et que cette comparaison s’applique pour des fréquences égales entre le processeur d’architecture K10 d’AMD et le Xeon d’Intel. De plus il ne s'agit là que de tests théoriques.

Début mai 2007, AMD a fait une nouvelle démonstration plutôt impressionnante de ses futurs K10[27]. C'est au CTO Technology Summit à Monterey, en Californie qu'AMD a dévoilé une machine disposant de deux processeurs K10 quadri-cœurs. La machine de 8 cœurs a été capable d'encoder à la volée, c'est-à-dire en temps réel, une vidéo 720p (1280 × 720) et une 1024p.

Famille de processeur

Toute la gamme d'AMD passera dans peu de temps à l'architecture K10. On retrouvera des dénominations connues et des nouveaux noms. L'Opteron pour serveur bi et quadri processeur connu sous le nom de code Barcelona sera le premier K10 à devoir faire ses preuves, un deuxième cœur Budapest viendra renforcer la gamme Opteron sur le marché des serveurs uni-processeurs. Le grand public aura le choix entre le Phenom X4 (Agena), et le Phenom X2 (Kuma). La dénomination Athlon 64 disparaissant (pour le haut de gamme), toute confusion entre les K8 et les K10 disparaît. On trouvera également des versions FX et Low power. Les Athlon x2 64 (Rana) constitueront l'offre bi-cœur d'entrée de gamme, les sempron (Spica) seront les seuls mono-cœur K10, et les Turion (Griffin) seront dédiés aux plates forme portables.

Tableau réalisé sur les informations de la roadmap AMD et de Clubic (Opteron) et (desktop)

65 nm

Serveur

Article connexe : Opteron.L'Opteron est la version du K10 destinée aux serveurs, et aux stations de travail. Les version SE sont les versions haut de gamme de la série au TDP de 120W, les versions standards ont un TDP de 95W et les version HE (High Efficiency) sont les versions qui bénéficient d'un TDP réduit à 68W.

modèles Opteron Nom du modèle Nombre de cœurs Fréquence TDP (W) Sockets compatibles Cache L1 Cache L2 Cache L3 Vitesse de Bus (MT/s) Date de sortie Opteron pour serveur mono-processeur. Budapest Opteron série 1000 Opteron 1252 4 2,1 GHz 95 AM2/AM2+ 4 × 128 kio 4 × 512 kio 2 Mio 5200 avril 2008 Opteron 1254 4 2,2 GHz 95 AM2/AM2+ 4 × 128 kio 4 × 512 kio 2 Mio 5200 avril 2008 Opteron 1256 4 2,3 GHz 95 AM2/AM2+ 4 × 128 kio 4 × 512 kio 2 Mio 5200 avril 2008 Opteron série 1000 SE Opteron 1258 SE 4 2,4 GHz 120 AM2/AM2+ 4 × 128 kio 4 × 512 kio 2 Mio 5200 2008 Opteron 1260 SE 4 2,5 GHz 120 AM2/AM2+ 4 × 128 kio 4 × 512 kio 2 Mio 5200 2008 Opteron pour serveur bi-processeur. Barcelona Opteron série 2000 hE Opteron 2244 hE 4 1,7 GHz 68 1207/1207+ 4 × 128 kio 4 × 512 kio 2 Mio 2000 ? Opteron 2246 hE 4 1,8 GHz 68 1207/1207+ 4 × 128 kio 4 × 512 kio 2 Mio 2000 ? Opteron 2248 hE 4 1,9 GHz 68 1207/1207+ 4 × 128 kio 4 × 512 kio 2 Mio 2000 ? Opteron 2250 hE 4 2,0 GHz 68 1207/1207+ 4 × 128 kio 4 × 512 kio 2 Mio 2000 ? Opteron série 2000 Opteron 2248 4 1,9 GHz 95 1207/1207+ 4 × 128 kio 4 × 512 kio 2 Mio 2000 Rentrée 2007 Opteron 2250 4 2,0 GHz 95 1207/1207+ 4 × 128 kio 4 × 512 kio 2 Mio 2000 Rentrée 2007 Opteron 2252 4 2,1 GHz 95 1207/1207+ 4 × 128 kio 4 × 512 kio 2 Mio 2000 avril 2008 Opteron 2254 4 2,2 GHz 95 1207/1207+ 4 × 128 kio 4 × 512 kio 2 Mio 2000 avril 2008 Opteron 2256 4 2,3 GHz 95 1207/1207+ 4 × 128 kio 4 × 512 kio 2 Mio 2000 avril 2008 Opteron 2258 SE 4 2,4 GHz 120 1207/1207+ 4 × 128 kio 4 × 512 kio 2 Mio 2000 avril 2008 Opteron 2260 4 2,4 GHz 120 1207/1207+ 4 × 128 kio 4 × 512 kio 2 Mio 2000 2008 Opteron série 2000 SE Opteron 2258 SE 4 2,4 GHz 95 1207/1207+ 4 × 128 kio 4 × 512 kio 2 Mio 2000 avril 2008 Opteron 2260 SE 4 2,5 GHz 120 1207/1207+ 4 × 128 kio 4 × 512 kio 2 Mio 2000 avril 2008 Opteron 2262 SE 4 2,6 GHz 120 1207/1207+ 4 × 128 kio 4 × 512 kio 2 Mio 2000 2008 Opteron pour serveur quadri processeur ou plus. Barcelona Opteron série 8000 hE Opteron 8248 hE 4 1,9 GHz 68 1207/1207+ 4 × 128 kio 4 × 512 kio 2 Mio 2000 ? Opteron 8250 hE 4 2,0 GHz 68 1207/1207+ 4 × 128 kio 4 × 512 kio 2 Mio 2000 ? Opteron série 8000 Opteron 8252 4 2,1 GHz 95 1207/1207+ 4 × 128 kio 4 × 512 kio 2 Mio 2000 avril 2008 Opteron 8254 4 2,2 GHz 95 1207/1207+ 4 × 128 kio 4 × 512 kio 2 Mio 2000 avril 2008 Opteron 8256 4 2,3 GHz 95 1207/1207+ 4 × 128 kio 4 × 512 kio 2 Mio 2000 avril 2008 Opteron 8258 4 2,4 GHz 95 1207/1207+ 4 × 128 kio 4 × 512 kio 2 Mio 2000 2008 Opteron série 8000 SE Opteron 8258 SE 4 2,4 GHz 120 1207/1207+ 4 × 128 kio 4 × 512 kio 2 Mio 2000 avril 2008 Opteron 8260 SE 4 2,5 GHz 120 1207/1207+ 4 × 128 kio 4 × 512 kio 2 Mio 2000 avril 2008 Opteron 8262 SE 4 2,6 GHz 120 1207/1207+ 4 × 128 kio 4 × 512 kio 2 Mio 2000 2008 Grand public

Article détaillé : Phenom.La nouvelle gamme desktop d'AMD se décompose donc en "Phenom FX" pour le très haut de gamme (qui sera sûrement un simple renommage d'Opteron), "Phenom X4" pour le haut de gamme et "Phenom X3" pour la moyenne gamme, "Athlon X2" et "Sempron" pour l'entrée de gamme AMD.

Les fréquences s'échelonnent entre 1 900 MHz et 2 800 MHz et le TDP entre 45 W et 89 W.

Le nombre de cœurs varie de 1 pour le "Sempron" à 4 pour le "Phenom FX" et le "Phenom X4" en passant par 3 pour le "Phenom X3" et 2 pour l' "Athlon X2".Modèle Nom de code Cœurs Fréquence Cache Révision TDP HyperTransport Socket L1 L2 L3 Phenom 9xxx Agena 4 1,8 à 2,6 Ghz 4 × 128 kio 4 × 512 Kio 2 Mio B2 - B3 65 à 140 W 1800 - 2000 Mhz AM2+ 8xxx Toliman 3 1,9 à 2,5 Ghz 3 × 128 kio 3 × 512 Kio 2 Mio B2 - B3 65 à 95 W 1800 Mhz AM2+ Athlon X2 7xxx Agena 2 2,5 à 2,8 Ghz 4 × 128 kio 4 × 512 Kio 2 Mio B3 95 W 1800 Mhz AM2+ Mobile

Pas de processeur K10 65 nm pour ordinateurs portables.

45nm

Serveur

Article détaillé : Opteron.Modèle Nom de code Cœurs Fréquence Cache Révision TDP HyperTransport Socket L1 L2 L3 Opteron 8400 Istanbul 6 2,1 à 2,8 Ghz 6 × 128 kio 6 × 512 kio 6 Mio D0 55 à 115 W 2400 Mhz F 8300 Shanghai 4 2,2 à 3,1 Ghz 4 × 128 kio 4 × 512 kio 6 Mio C2 68 à 137 W 1000 MHz, 2200 Mhz F 2400 Istanbul 6 2,0 à 2,8 Ghz 6 × 128 kio 6 × 512 kio 6 Mio D0 115 W 2400 Mhz F 2300 Shanghai 4 2,3 à 3,1 Ghz 4 × 128 kio 4 × 512 kio 6 Mio C2 60 à 137 W 1000 MHz, 2200 Mhz F Opteron en prévision Magny-Cours 12 12 × 128 kio 12 × 512 kio 2 × 6 Mio G34 (en) Sao Paolo 6 6 × 128 kio 6 × 512 kio 6 Mio G34 (en) Grand public

Modèle Nom de code Cœurs Fréquence Cache Révision TDP HyperTransport Socket L1 L2 L3 Phenom II X4 9xx Deneb 4 2,6 à 3,4 Ghz 4 × 128 kio 4 × 512 kio 6 Mio C2 65 à 140 W 2000 Mhz AM3 X4 8xx Deneb 4 2,5 à 2,8 Ghz 4 × 128 kio 4 × 512 kio 4 Mio C2 95 W 2000 Mhz AM3 X3 7xx Heka 3 2,4 à 3,0 Ghz 3 × 128 kio 3 × 512 kio 6 Mio C2 65 à 95 W 1800 Mhz AM3 X2 5xx Callisto 2 3,0 à 3,1 Ghz 2 × 128 kio 2 × 512 kio 6 Mio C2 80 W 1800 Mhz AM3 Athlon II X4 6xx Propus 4 2,2 à 2,8 Ghz 4 × 128 kio 4 × 512 kio - C2 45, 95 W 1800 MHz AM3 X3 4xx Rana 3 2,2 à 2,9 Ghz 3 × 128 kio 3 × 512 kio - C2 45, 95 W 1800 MHz AM3 X2 2xx Regor 2 2,7 à 3,0 Ghz 2 × 128 kio 2 × 1 Mio - C2 45 à 65 W 2000 Mhz AM3 Sempron 1xx Sargas 1 2,7 Ghz 1 × 128 kio 1 Mio - C2 45 W 2000 MHz AM3 Mobile

Avec le Turion Griffin, AMD proposera un K10 très allégé qui ne disposera que des améliorations énergétiques du DICE. Avec son Griffin, AMD proposera également une plateforme: Puma. Elle utilisera un cœur graphique supportant le directX 10 et un UVD (Universal Video Decoder).

Modèle Nom de code Cœurs Fréquence Cache Révision TDP HyperTransport Socket L1 L2 L3 Turion II ? 2 2,4 à 2,6 Ghz 2 × 128 kio 2 × 1 Mo - [28] 2 2,0 à 2,3 Ghz 2 × 128 kio 2 × 512 kio - 1 2,0 Ghz 128 kio 512 kio - Liens internes

- Phenom

- AMD K8

- Athlon 64

- Socket AM2+

- Socket AM3

- Socket F

- DDR2 SDRAM

- HyperTransport

- Unité de calcul en virgule flottante

- Unité arithmétique et logique

- Streaming SIMD Extensions

Liens externes

- (en) Article Technique sur RWT

- (en) Article de The Inquirer, qui rapporte les propos de Giuseppe Amato (Technical Director, Sales and Marketing EMEA de AMD)

- (en) Further AMD next-gen specs roll out (The Inquirer, liste des processeurs K10 au lancement)

- (en) December 2006 Analyst Day d'AMD: roadmap officielle d'AMD.

- (en) Barcelona Architecture: AMD on the Counterattack (revue détaillée de l'architecture K10 par anandtech)

- (en) Anandtech, CeBIT 2007: Storage & Servers - AMD, performances et indications sur le Barcelona au CeBIT 2007.

- (fr) les 21 déclinaisons desktop du K10

- (fr) Architectures des processeurs, version préliminaire et ancienne (2001) d'un cours de l'IRISA (Institut de recherche en informatique et systèmes aléatoires) mais très complet.

- (fr) AMD K8 - Partie 3 : Architecture, comprendre l'architecture K8 permet de comprendre l'architecture K10 qui en est une grande évolution plus qu'une révolution.

- (fr) Nouvelle nomenclature AMD (InfoMars.fr)

Notes et références

- ↑ interview de Giuseppe Amato et de Philip G. Eisler par syndrome-oc

- ↑ AMD and IBM to Jointly Develop Advanced Chip Technologies

- ↑ « Faisant suite à une commande pour un montant minimal de 150 millions de dollars sur l’année calendaire 2006, AMD s’est engagé sur une valeur minimale de 350 millions de dollars pour une période de 15 mois qui débutera en janvier 2007. Cette commande s’inscrit dans le cadre du contrat pluriannuel de fourniture de plaques SOI 300mm UNIBOND™ utilisant la technologie Smart Cut™, propriété exclusive de Soitec. Les plaques seront livrées à AMD et à son partenaire fondeur. » Premier semestre 2006-2007 : Soitec annonce une forte amélioration de ses résultats, une visibilité accrue et des perspectives favorables

- ↑ « Ces processeurs [Athlon 64 EE] 65 nm sont tous produits dans l'usine Fab 36 d'AMD, toujours selon le procédé SOI. » AMD lance ses Athlon 64 X2 Energy Efficient en 65 nm

- ↑ Fab 36 devrait tourner à plein régime vers 2008, ce qui portera la production annuelle de processeurs AMD à 100 millions d’unités. AMD : Fab 36 est sortie de terre

- ↑ AMD favorise l’avènement de l’informatique nouvelle génération avec le passage à la technologie de production en 65 nm

- ↑ AMD et IBM utiliseront la lithographie par immersion pour passer le cap des 65nm

- ↑ Le contrôleur mémoire intégré, AMD K8 - Partie 3 : Etude de l'Architecture

- ↑ Athlon 64 & Sempron socket AM2, conclusion

- ↑ AM3, 45nm et DDR3 chez AMD en 2008

- ↑ Nvidia MCP72: PCI-E 2.0 & HT 3.0

- ↑ Chipsets VIA KT/KM960 pour AM2+

- ↑ Tous les futurs chipsets 7xx d'AMD

- ↑ Interview AMD, plein de nouvelles infos sur Barcelona

- ↑ C'est dans ces 60 millions de transistors que l'on doit trouver des améliorations et de nouvelles fonctions.

- ↑ clones du SSE4 introduit par Intel dans ses Conroe Extending the World’s Most Popular Processor Architecture (papier officiel d'Intel).

- ↑ « Les instructions qui se décodent en plus de deux µOPs, dites complexes, sont décodées par la ROM interne, ce qui nécessite davantage de temps. On dit alors que ces instructions sont microcodées. » AMD K8 - Architecture

- ↑ en français dans le désordre ce qui réduit le temps d'attente des instructions.

- ↑ Ce qui permet de plus facilement revenir sur les erreurs de prédiction. « La pile est une zone mémoire destinée à stocker les paramètres lors de l'appel de sous-parties d'un programme. » Etude détaillée du Pentium-M - Un traitement des instructions plus efficace

- ↑ « Les opérations nécessaires à la gestion de la pile ne sont plus ici traitées par les unités génériques de traitement des instructions, mais par une unité exclusivement dédiée à cette tâche, et qui porte justement le nom de Dedicated Stack Manager. Cette unité permet, toujours selon Intel, de réduire de 5% le nombre de micro-opérations traitées par le pipeline. » Etude détaillée du Pentium-M - Un traitement des instructions plus efficace

- ↑ « Cache des processeurs gérant une mémoire virtuelle contenant la correspondance entre les adresses logiques de la mémoire utilisée et les adresses physiques correspondantes. » Dictionnaire francophone des acronymes, sigles et abréviations informatiques. Cette augmentation du TLB ne devrait profiter qu'au domaine serveur.

- ↑ Les améliorations de performance grâce à une réduction de latence entre RAM et cache L2 ou L3 pourraient être importantes, d'après Anandtech: « it really helps the entire chip improve performance and can do a good job of spotting trends that would positively impact all cores »

- ↑ « L’OS hôte aura ainsi l’illusion que c’est lui qui gère la mémoire. Selon AMD, Nested Paging réduira le temps de compilation des informations de 43 %. Intel devrait proposer une technologie équivalente au second semestre sous le nom de "Extended Paging" » Intel et AMD virtualisent la mémoire et les entrées/sorties

- ↑ article de pcinpact relatant la démonstration

- ↑ page officielle d'AMD (attention RTC, site très lourd)

- ↑ article de clubic quant aux dernières performances du Barcelona.

- ↑ AMD fait la démonstration de ses Phenom, et par deux !

- ↑ AMD lance Tigris, les Turion II passent au K10

- Portail de l’électricité et de l’électronique

- Portail de l’informatique

Catégorie : Microprocesseur x86 AMD - Généralités.

Wikimedia Foundation. 2010.