- Sse

-

Streaming SIMD Extensions

Streaming SIMD Extensions, généralement abrégé SSE, est un jeu de 70 instructions supplémentaires pour microprocesseurs x86, apparu en 1999 sur le Pentium III en réponse au 3DNow! d'AMD apparu 1 an plus tôt. Le fonctionnement est de type SIMD.

Il a été d'abord dévoilé sous le nom KNI signifiant « Katmai New Instructions » (Nouvelles instructions Katmai en anglais, Katmai étant le nom de code pour la première version du cœur du Pentium III). Pendant le projet Katmai, Intel désirait le distinguer de leurs lignes de produit précédentes et particulièrement de leur produit phare, le Pentium II. AMD ajouta le support d'instructions SSE, avec ses processeurs Athlon XP. Il fut ultérieurement renommé ISSE, ce qui signifie « Internet Streaming SIMD Extensions » (Extensions SIMD pour flux Internet en anglais), puis SSE.Intel a été globalement déçu par leur premiers travaux sur les SIMD et MMX IA-32. Le MMX avait deux problèmes principaux : Il réutilisait des registres à virgule flottante existants, rendant le CPU incapable de fonctionner simultanément en virgule flottante et en donnée SIMD et ne fonctionnait que sur les entiers.

Sommaire

Registres

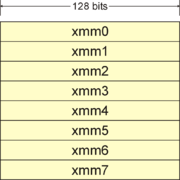

Le SSE a originellement ajouté huit nouveaux registres 128 bits nommés XMM0 à XMM7. Les extensions x64 d'Intel et AMD ajoutent huit nouveaux registres de XMM8 à XMM15. Il y a également un nouveau registre 32 bits de contrôle/statut nommé MXCSR.

Chaque registre compacte ensemble quatre nombre flottants simple précision 32 bits. Les opérations SIMD entières peuvent toujours être effectuées par les huit registres 64 bits MMX.

Instructions SSE

Le SSE a à la fois introduit des instructions scalaires et de virgule flottante compactée.

Instructions à virgule flottante

- Déplacement de donnée de mémoire à registre / Registre à mémoire / Registre à registre.

- Scalaire - MOVSS

- Compacté - MOVAPS, MOVUPS, MOVLPS, MOVHPS, MOVLHPS, MOVHLPS

- Arithmétique

- Scalaire - ADDSS, SUBSS, MULSS, DIVSS, RCPSS, SQRTSS, MAXSS, MINSS, RSQRTSS

- Compacté - ADDPS, SUBPS, MULPS, DIVPS, RCPPS, SQRTPS, MAXPS, MINPS, RSQRTPS

- Comparaison

- Scalaire - CMPSS, COMISS, UCOMISS

- Compacté - CMPPS

- Mélange de données et depactage.

- Compacté - SHUFPS, UNPCKHPS, UNPCKLPS

- Conversion de type de donnée

- Scalaire - CVTSI2SS, CVTSS2SI, CVTTSS2SI

- Compacté - CVTPI2PS, CVTPS2PI, CVTTPS2PI

- Opération logiques bit à bit

- Compacté - ANDPS, ORPS, XORPS, ANDNPS

Instructions entières

- Arithmétiques

- PMULHUW, PSADBW, PAVGB, PAVGW, PMAXUB, PMINUB, PMAXSW, PMINSW

- Mouvement de données

- PEXTRW, PINSRW

- Autres

- PMOVMSKB, PSHUFW

Autres instructions

- Gestion MXCSR

- LDMXCSR, STMXCSR

- Gestion de la mémoire et du cache

- MOVNTQ, MOVNTPS, MASKMOVQ, PREFETCH0, PREFETCH1, PREFETCH2, PREFETCHNTA, SFENCE

Exemple

Le simple exemple suivant démontre les avantages de l'utilisation du SSE.

En considérant une opération comme l'addition vectorielle, qui est très souvent utilisé dans les applications graphiques informatique. Le x87 requiert quatre instructions d'addition flottantes pour additionner entre eux deux vecteurs de dimension 4 à simple précision.

vec_res.x = v1.x + v2.x;

vec_res.y = v1.y + v2.y;

vec_res.z = v1.z + v2.z;

vec_res.w = v1.w + v2.w;

Cela correspond à quatre instructions

FADDdu x87 en code objet. Alors que le pseudo-code suivant montre qu'une seule instruction 128 bit (addition compacte) peut remplacer les quatre instructions d'addition scalaire.movaps xmm0,adresse-de-v1 ;xmm0=v1.w | v1.z | v1.y | v1.x

addps xmm0,adresse-de-v2 ;xmm0=v1.w+v2.w | v1.z+v2.z | v1.y+v2.y | v1.x+v2.x movaps adresse-du-vec_res,xmm0

Évolutions

- Le SSE2 créé pour le pentium 4 ajoute des instructions flottantes double précision (64 bits) et étend les instructions MMX avec des opérations sur les registres XMM 128 bits.

- Le SSE3 sur le Pentium IV Prescott, ajoute des instructions mathématiques orientées DSP et quelques instructions de gestion de processus.

- Le SSSE3 ajoute 16 nouveaux opcodes qui incluent la permutation des octets dans un mot, la multiplication des nombre à virgule fixe 16 bits avec un arrondissement correct et des instructions d'accumulation dans un mot. SSSE3 est souvent confondu avec SSE4 car ce terme a été utilisé pendant la phase de développement de la microarchitecture.

- Le SSE4 est une autre avancée majeure, ajoutant une instruction de produit scalaire, de nombreuses instructions d'additions entières, une instruction

popcntet d'autres instructions. SSE4 arrête le support des registres MMX. Le SSE4 est supporté par la version 'Penryn' de la microarchitecture Core 2[1],[2]. - Le SSE5 prévu initialement pour mi-août 2007 par AMD, permet, comme dans les processeurs RISC, de préciser dans l'instruction un troisième registre destination, ce qui permet d'économiser un bon nombres d'instructions et devrait intrinsèquement accélérer les calculs. Auparavant, il fallait d'abord copier le contenu du registre destination dans un nouveau registre afin de ne pas détruire les informations précédentes[3],[4].

Voir aussi

Références

- ↑ (en)[1]

- ↑ (en)[2]

- ↑ (en)AMD plots single thread boost with x86 extensions sur theregister.co.uk

- ↑ (en)128-Bit SSE5 Instruction Set sur developer.AMD.com

Catégories : Microprocesseur | SIMD - Déplacement de donnée de mémoire à registre / Registre à mémoire / Registre à registre.

Wikimedia Foundation. 2010.