- PCI-E

-

PCI Express

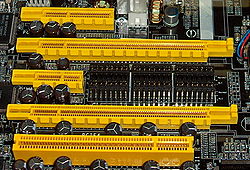

Port PCI Express (de haut en bas : ×4, ×16, ×1 et ×16), comparé au traditionnel Port PCI 32-bit (en bas)

Port PCI Express (de haut en bas : ×4, ×16, ×1 et ×16), comparé au traditionnel Port PCI 32-bit (en bas)

Le PCI Express, abrégé PCI-E ou PCIe (anciennement 3GIO, 3rd Generation Input/Output) est un standard développé par Intel et introduit en 2004. Il spécifie un bus local série (« bus PCI express ») et un connecteur qui sert à connecter des cartes d’extension sur la carte mère d’un ordinateur. Il est destiné à terme à remplacer tous les connecteurs d’extension d’un PC, dont le PCI et l’AGP (en 2009 l’AGP a disparu au profit du PCIe sur tous les nouveaux modèles de cartes mère).

Sommaire

Une évolution du PCI

Un avantage du PCI Express est d’être dérivé de la norme PCI (Peripheral Component Interconnect), ce qui permet aux constructeurs d’adapter simplement leurs cartes d’extension existantes, puisque seule la couche matérielle est à modifier. D’autre part, il est suffisamment rapide pour pouvoir remplacer non seulement le PCI classique mais aussi l’AGP, un port rapide pour cartes graphiques. Il serait même envisagé dans l’avenir d’y connecter des périphériques externes.

Contrairement au PCI qui est relié au southbridge de la carte mère, le PCI Express est relié au northbridge.

Alors que le PCI utilise un unique bus de largeur 32 bit bidirectionnel alterné (half duplex) pour l’ensemble des périphériques, le PCI Express utilise une interface série (de largeur 1 bit) à base de lignes bidirectionnelles. On pourra ainsi parler d’une carte mère possédant 20 lignes PCIe. Une ligne permet théoriquement des échanges full duplex à 250 Mo/s pour la version 1.1 du protocole. Les différents périphériques communiquent alors par échange de paquets et l’arbitrage du bus PCI est remplacé par un commutateur. Le principe de fonctionnement est semblable à de la commutation de paquets selon un modèle à quatre couches :

- couche logicielle : codage/décodage des paquets de données.

- couche transaction : rajout/suppression d’un en-tête de début et d’un en-tête de séquencement ou de numérotation du paquet.

- couche liaison : rajout/suppression d’un code de correction d’erreur (contrôle de redondance cyclique).

- couche physique : transmission du paquet (transmission série "point à point").

On parle de ports PCIe ×1, ×2, ×4, ×8, ×16 et ×32 pour différencier les ports en fonction du nombre de connecteurs de ligne dont ils disposent (respectivement 1, 2, 4, 8, 16 ou 32 lignes maximum). Un port x32 permet d'atteindre en théorie un débit de 8 Go/s, soit 4 fois le débit des ports AGP[1].

Un port ×16 par exemple peut n’être relié qu’à 8 lignes PCIe ; il devra tout de même avoir un apport de puissance electrique nécessaire aux cartes ×16. Une carte d’extension ×16 fonctionnera sur ce port (mais probablement avec des performances non optimales), car le protocole PCI-e prévoit la négociation mutuelle du nombre de lignes maximum supportée par les deux entités communiquante. De même, une carte (exemple : ×1) peut être connectée et fonctionnera correctement sur un port plus grand (exemple : ×1, ×2, …, ×32).

Voir aussi

Articles connexes

Sources

- Andrew Tannenbaum, L’achitecture des ordinateurs, Éd. Pearson

Notes et références

- Portail de l’informatique

Catégories : Bus informatique | Connectique | Carte mère

Wikimedia Foundation. 2010.