- Inter Integrated Circuit Bus

-

I²C

I²C (pour Inter Integrated Circuit Bus) est le nom du bus historique, développé par Philips pour les applications de domotique et d’électronique domestique au début des années 1980, notamment pour permettre de relier facilement à un microprocesseur les différents circuits d’une télévision moderne. Ce bus porte parfois le nom de TWI (Two Wire Interface) chez certains constructeurs.

Sommaire

Présentation

I²C est un bus qui a émergé de la « guerre des standards » lancée par tous les acteurs du monde électronique. Ainsi, dans votre téléviseur, tous les ensembles sont sur un bus I2C (récepteur de la télécommande, réglages des amplificateurs basses fréquences, tuner, horloge, gestion de la prise péritel, etc.).

Il existe d’innombrables périphériques exploitant ce bus, il est même implémentable par logiciel dans n’importe quel microcontrôleur. Le poids de l’industrie de l’électronique grand public a permis des prix très bas aux nombreux composants.

Les données sont transmises en série de manière synchrone ; cela signifie que les informations sont envoyées à la suite sur le même fil (une donnée par coup d'horloge), contrairement à une communication parallèle où plusieurs données sont envoyées en même temps, mais sur différents fils. Par nature les protocoles séries sont donc, à fréquence constante, beaucoup plus lents qu'une connexion parallèle, cependant l'I²C convient tout à fait à toutes les applications où la vitesse n'est pas primordiale.[réf. nécessaire]

Fonctionnement

Un bus I²C contient trois fils :

- un signal de donnée (SDA) ;

- un signal d'horloge (SCL) ;

- un signal de référence (masse).

Le périphérique qui gère la communication est le maître, c'est lui qui génère l'horloge (SCL) et qui envoie les données (SDA) mis à part l'acknowledge (acquittement en français).

L'horloge n'est pas une « véritable » horloge, dans le sens ou les ton et toff peuvent varier les uns par rapport aux autres.

L'acquittement est un 'bit' envoyé par le composant esclave pour indiquer qu'il a bien reçu toutes les données ; si c'est le cas l'esclave impose le niveau 0, sinon la résistance de pull-up maintient la ligne à 1, on dit alors qu'il n'y a pas d'acknowledge. (NACK qui veut dire "non acknowledge" en anglais)

Au début de la communication SDA passe de 1 à 0 alors que SCL reste à 1, c'est le StartBit.

Après avoir imposé la condition de départ, le maître passe SCL à 0 puis applique ensuite sur SDA le bit de poids fort.

Il latch (verrouille) la donnée en appliquant pendant un instant un niveau #1 sur la ligne SCL.

Lorsque SCL revient à #0, il recommence l'opération avec le bit inférieur jusqu'à ce que l'octet complet soit transmis.

Il redéfinit ensuite SDA comme une entrée et scrute son état ; l'esclave doit alors imposer un niveau #0 pour signaler au maître que la transmission s'est effectuée correctement, c'est l'acknowledge, la communication peut donc continuer.

Si l'esclave n'envoie pas l'acknowledge les résistances de pull-up maintiennent la ligne à #1. La communication peut alors être arrêtée, ou reprendre à zéro (dépend de la configuration), c'est le rôle du bit de STOP StopBit.

Le StopBit indiquant la fin de la transmission par le maître est effectué en appliquant un passage de 0 à 1 de SDA alors que SCL reste lui à 1.Le premier octet envoyé est l'adresse, il est composé de 7bits variable selon le composant et du bit de read/write (0 pour write, 1 pour read).

Le second octet peut être le byte de contrôle sur certains composants, ou directement la donnée.

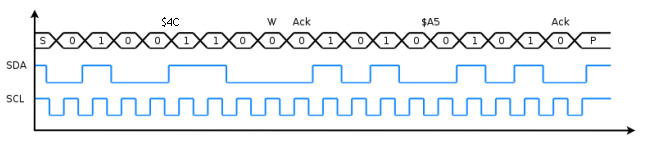

Exemple de communication I²C:

La communication commence par le StartBit

puis l'adresse, (sur 8bits $4C) avec bit de read/write à 0

l'acknowledge (Ack)

un octet de données ($A5)

de nouveau l'acknowledge (Ack)

et enfin le StopBit.L'adressage

Plusieurs composants peuvent être branchés sur le même bus I2C. Pour que l'information aille au bon endroit chaque composant possède sa propre adresse.

Elle est composée d'une partie fixe imposée par le constructeur, d'une partie configurable de façon matérielle par l'utilisateur, et du bit de read/write qui définit le sens de la transmission (0 pour écriture, 1 pour lecture).

Support des systèmes d'exploitation

Technologies dérivées

I²C est à la base de l’ACCESS.bus, de l’interface VESA Display Data Channel (DDC), du System Management Bus (SMBus), et de l’Intelligent Platform Management Bus (IPMB, l’un des protocoles de l’IPMI). Ces implantations présentent des différences dans les tensions et les fréquences d’horloge, et peuvent avoir des interrupt lines (IRQ).

Voir aussi

Lien externe

- Portail de l’électricité et de l’électronique

Catégorie : Protocole de communication

Wikimedia Foundation. 2010.