- Reconfiguration dynamique des FPGAs

-

La Re-configuration dynamique des FPGAs consiste à changer la programmation de ces circuits logiques programmables alors qu'ils sont en activité.

A l'origine, ces circuits logiques programmables ont été conçus pour permettre de réaliser très rapidement des fonctions logiques plus ou moins complexes, c'est-à-dire directement opérées par un circuit électronique. Pour cela, le FPGA permet de définir et de redéfinir à volonté une configuration arbitraire de chemins entre des portes logiques élémentaires. Néanmoins, la redéfinition d'un circuit logique au sein du FPGA est une opération singulière, supposée peu fréquente, et réalisée alors que le système informatique au sein duquel il prend place est « hors-fonction ».

De nouveaux développements de cette technologie ont permis d'envisager la configuration et la re-configuration de circuits logiques programmables sans en interrompre le fonctionnement. Cette approche ouvre de nouvelles perspectives dans la réduction de la taille et de la consommation des FPGAs tout en offrant de nouvelles opportunités à leur exploitation.

Sommaire

Origine et Architecture des FPGAs

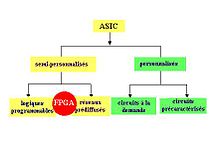

Les FPGAs se traduisent en français par "circuits prédiffusés programmables". Les circuits prédiffusés sont des circuits partiellement préfabriqués. Ils contiennent un ensemble d'éléments (transistors, diodes, résistances, capacités, etc...) qui ne sont pas interconnectés entre eux. Contrairement aux circuits prédiffusés conventionnels, les circuits prédiffusés programmables ne demandent pas de fabrication spéciale en usine, ni de matériels de développement coûteux[1].

Les FPGAs ont été inventés et commercialisés la première fois par la société Xilinx en 1985. Ils sont de la famille des ASICs (Application Specific Integrated Circuit). Ils se situent entre les réseaux logiques programmables et les circuits prédiffusés. C'est donc des composants standard combinant la densité et les performances d'un circuit prédiffusé avec la souplesse due à la re-programmation des PLD (programmable logic device : circuit logique programmable)[1].

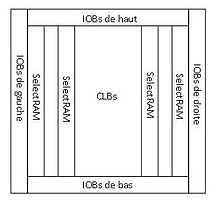

Sur le marché les fondateurs (Xilinx, Altera, Atmel) ont développé plusieurs familles de FPGA, concurrentes ou complémentaires, parfois moins performantes, parfois mieux adaptées. L'architecture, retenue par Xilinx se présente sous forme de deux couches :- une couche appelée circuit configurable,

- une couche de mémoire SRAM (SelectRAM)[1].

La couche dite 'circuit configurable' est constituée d'une matrice de blocs logiques configurables CLB (Configurable Logic Block). Les CLBs permettent de réaliser des fonctions combinatoires et des fonctions séquentielles. Tout autour de ces CLBs, on trouve des blocs entrées/sorties IOB (Input/Output Block) dont le rôle est de gérer les entrées-sorties réalisant l'interface avec les modules extérieurs.

La couche SRAM est un ensemble de blocs de mémoire RAM configurables de différentes manières. Leur capacité est de 18KB. Les blocs de la SRAM peuvent être mis en cascade pour réaliser de larges zones de stockage enfouies dans le FPGA.

La mise au point de la configuration d'un FPGA consiste dans un premier temps à décrire ses données de configuration sous forme d’une succession de bits qu'on appelle bitstream/fichier de configuration. Ce bitstream est stocké dans une ROM externe au FPGA. Ainsi à la mise sous tension du FPGA, sa mémoire SRAM est chargé à partir de cette ROM et la configuration est prise en compte. Ensuite une vérification est effectuée pour tester si le fonctionnement réel correspond bien à l'attente du concepteur[1].La configuration d'un FPGA permet d'établir des interconnexions entre ses CLB et ses IOB. Pour cela, ils disposent de la mémoire SRAM interne dans laquelle sera écrit le fichier de configuration[1].

Certaines architectures de FPGA en fonction des constructeurs peuvent contenir :

- des BRAM (Bloc RAM) qui représentent un module de mémoire destiné aux grands éléments de stockage

- un VersaRing qui est un réseau additionnel de lignes d’interconnexion entre les IOB et les CLB: cela permet de changer facilement la configuration interne du circuit tout en gardant le même brochage

- à chaque signal d’horloge global il y a un DLL (Delay-locked loop) qui permet de modifier la phase du signal, pour améliorer les caractéristiques des flux des données en sortie.

Re-configuration dynamique

La logique re-configurable est une branche émergente de l'architecture informatique qui cherche à construire des systèmes informatiques flexibles et dynamiques. C'est-à-dire des systèmes ayant la propriété de pouvoir être modifiés après leur conception et pendant leur exécution, chose qui permet atteindre des niveaux de performance très élevés[2]. Au cœur de ces systèmes informatiques est le FPGA, ce circuit peut être facilement configuré et re-configuré par l'utilisateur final. Le FPGA possède un certain nombre d'interfaces de configuration qui sont utilisés pour télécharger les données de configuration afin de pouvoir changer à tout moment son fonctionnement[3].Que doit-on en attendre ?

Le principal intérêt d’un système reconfigurable est de pouvoir changer à tout moment les algorithmes exécutés par le matériel, rappelons que cela est fait depuis bien longtemps par les microprocesseurs[4]. La reconfiguration dynamique n’a donc de sens que si elle s’accompagne de performances (à coûts identiques) bien supérieures à celles des structures programmées classiques. Or, on constate que les processeurs conventionnels ou les DSP (Pentium, c60, c80, sharc) sont capables d’exécuter un algorithme de traitement d’images relativement complexe en temps réel. Ce qui semble discréditer quelque peu la technologie FPGA[4]. On remarque cependant que les processeurs sont alors en limite d’utilisation : boucle interne de deux ou trois cycles optimisée au cycle près ; toute modification même minime remet en cause la faisabilité globale sous contrainte temps réel. D’autre part, ce résultat est obtenu pour des fréquences de travail supérieures d’un facteur dix par rapport aux solutions FPGA. Cependant la re-configuration dynamique est une solution architecturale et technologique qui ne permet pas des gains en vitesse de traitement, mais qui réduit la complexité de circuit nécessaire à une application donnée[4].

Dans la suite on détaillera les approches de la re-configuration dynamique qui sont : la re-configuration pendant l'exécution du FPGA (run-time re-configuration), l'auto-reconfiguration.La re-configuration pendant l’exécution (RTR)

C'est la capacité d’un FPGA à re-configurer ses ressources pendant l’exécution d’une application. Ce type de re-configuration devient une exigence de plus en plus importante sur les marchés de nombreux utilisateurs, en particulier les utilisateurs militaires qui doivent s'adapter rapidement à différentes menaces et l'évolution des formes d'onde de communication.

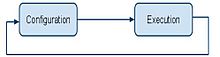

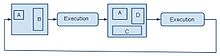

La RTR peut re-configurer les FPGAs plusieurs fois pendant l'opération normale d'une seule application comme indiqué sur la figure 4[5].

Problématique propre à la RTR

La nature dynamique du matériel présente deux nouveaux problèmes de conception, face à une RTR.

Le premier est la division de l’algorithme de l'application (Exemple : une application de traitement d'images)en segments temporaires exclusifs qui n'ont pas besoin de s’exécuter simultanément. Ce processus de division est appelé partitionnement temporaire[6]. Typiquement, on décompose l'algorithme en phases distinctes. Pour chacune de ces phases on définit un fichier de configuration. Ces fichiers de configurations sont ensuite téléchargés dans le FPGA comme requis par l'application[6].

La division temporaire exige jusqu’à présent une participation ennuyeuse et prédisposée aux erreurs de l’utilisateur final de l’application[6].Le second problème de conception consiste à coordonner le comportement entre les configurations des applications RTR. Ce comportement se manifeste sous la forme de communication inter-configuration, ou la transmission des résultats intermédiaires d'une configuration à l'autre. Cela arrive pendant la progression normale de l'application. Chaque configuration traitera des données et produira ensuite un certain résultat intermédiaire qui sert d'entrée à la configuration suivante. Cela a un effet énorme sur le processus de conception, parce que toutes les configurations doivent être soigneusement conçues, de tel sorte qu'elles marchent à travers les différentes phases de l’application et communiquent des résultats intermédiaires entre elles[6].

Principe de fonctionnement de la RTR

Il existe deux approches de base qui peuvent être utilisées pour la mise en œuvre de la RTR : l'approche globale et partielle. Ces deux approches configurent toutes le FPGA lors de l'exécution de l’application. La principale différence entre elles est la façon dont le matériel dynamique est alloué[7].

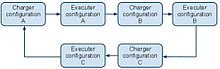

- RTR globale: La RTR globale alloue toutes les ressources du FPGA dans chaque étape de re-configuration. Plus précisément, les RTRs globales sont divisées en différentes phases temporaires, où chaque phase est implémentée comme une configuration unique du système qui occupe toutes les ressources du FPGA. Au moment de l'exécution, à chaque phase d'avancement de l'application (pour laquelle la re-configuration du FPGA se fait), toutes les ressources du FPGA sont chargées avec les configurations associées à cette phase[7].

Comme exemple la figure 5 montre comment une seule application est créée à partir de 3 configurations (A, B, C). L’application exécute séquenciellement les trois configurations du matériel temporairement disjointes.

Mise en œuvre d’un RTR globale

Dans la mise en œuvre de la RTR globale, la tâche principale de la conception est de diviser temporairement l’algorithme de l'application en partitions à peu près de même taille. Cette division permet d'utiliser efficacement des ressources re-configurables. Comme expliqué dans la partie des problématiques chaque partition est associé à un fichier de configuration. Cependant, l'étape de partitionnement temporaire est itératif c'est-à-dire que le concepteur doit créer une partition initiale, puis réitérer ensuite tant sur la conception que la division, jusqu’à ce que les tailles des partitions soient approximativement égales[7].

Le principal inconvénient de cette approche est la nécessité d'une même taille de partitions temporaires. S’il n’est pas possible de faire cette division équitable des partitions, il en résultera une inefficacité d’utilisation des ressources du FPGA[7].Une fois qu'une application a été temporairement partitionnée, un moyen doit être prévu pour soutenir la communication inter-configuration. Ceci parce que chaque phase occupe toutes les ressources re-configurables. Typiquement les partitions sont organisées de sorte que chaque phase de l’application calcule un certain résultat intermédiaire. Ce résultat intermédiaire est placé dans la mémoire ou un registre du FPGA. Lorsque la phase suivante est chargée commencera l'opération en lisant ce résultat intermédiaire et continuera ensuite à calculer le résultat suivant. Ce processus "chargement et exécution" continue jusqu'à ce que l'application soit terminée[7]. L'avantage principal de la RTR globale est sa simplicité relative. Parce que les divisions de l'application sont à granularité grosse[7].

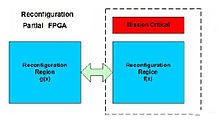

- RTR partielle : est le processus de configuration d'une partie du FPGA, tandis que l'autre partie est toujours fonctionnelle. Elle est réalisée pour permettre au FPGA de s'adapter aux algorithmes de changement de matériel, améliorer la tolérance aux pannes, améliorer les performances ou de réduire la consommation d'énergie. La RTR partielle est particulièrement utile certains circuits du FPGA qui ne doivent pas être perturbés alors que d'autres sont en cours de redéfinition. Les circuits ne devant pas être perturbés sont appelés environnement critique (mission critical)[8]

La partie du FPGA à redéfinir est divisée en régions de re-configuration, et une nouvelle succession de bits de configuration (bitstream / fichier de configuration) doit être créée pour chaque région. Le FPGA continue à utiliser les fonctions essentielles à l’environnement critique et à répondre aux exigences de l'interface externe tandis que les régions de re-configuration sont reprogrammées pour fournir des fonctionnalités différentes[8]

Une analogie peut être faite entre le changement de contexte avec un microprocesseur, où l'état actuel est conservé, afin de passer à un processus différent. Cependant, dans le cas du FPGA le changement de contexte se fait au niveau matériel et non logiciel[8].

La RTR partielle prend une approche encore plus flexible que la re-configuration globale. Cette flexibilité permet à des ressources matérielles de s’adapter au profil d'exécution de la demande avec une granularité plus fine que celle de la RTR globale[7].

Considérant que la RTR globale met en œuvre le processus d'exécution par un chargement important des partitions, la RTR locale n’a besoin de charger que les fonctionnalités nécessaires à chaque étape dans le temps. Cela peut réduire la quantité de temps consacré au téléchargement des configurations. Et peut conduire à une plus efficace exécution du matériel alloué[9].Mise en œuvre d’une RTR partielle

L'avantage principal que la RTR partielle a sur celle globale est la capacité de créer les opérateurs fonctionnels à une granularité fine qui font l'utilisation plus efficace des ressources du FPGA. Ceci est important pour les applications qui ne sont pas faciles à diviser en partitions de tailles égales. Toutefois, cet avantage peut entraîner une pénalité de conception très élevée en raison de la flexibilité accrue et de la complexité du système. Contrairement à la RTR globale où les interfaces de circuits restent fixes entre les configurations, la RTR partielle permet à ces interfaces de changer à chaque configuration[9].Modèles et outils d'abstraction proposés

Le PARBIT

La re-configuration partielle pendant l’exécution est une tâche difficile, il est nécessaire d'isoler une zone spécifique à l'intérieur du FPGA et télécharger les bits de configuration dedans.

L'outil PARBIT (PARtial BItfile Transformer) est un logiciel développé pour transformer les bitstreams de configuration initiale du FPGA en des bitstreams partiels. Avec cet outil. Il est possible de définir une zone partielle re-configurable à l'intérieur du FPGA et télécharger les bitstreams partiels dans cette zone[10].

Pour restructurer les bitstreams partiels de la re-configuration, l'outil utilise le flux de bits original (bitstream) et les paramètres donnés par l'utilisateur. Ces paramètres comprennent un bloc de coordonnées de la logique mise en œuvre sur le FPGA d'origine, les coordonnées de la zone pour la partie cible à programmer dans le FPGA et les options de programmation. Afin de générer les bitstreams partiels, le PARBIT lit les configurations du flux de bits original, copies seulement les bits relatifs à la zone définie par l'utilisateur[10]. Il génère alors de nouvelles valeurs pour les registres de configuration de la zone de re-configuration partielle. Il existe deux modes que l'utilisateur peut utiliser pour spécification des paramètres utilisateur :- Dans le premier, appelé Slice mode, l'utilisateur spécifie une section contenant une ou plusieurs colonnes CLB. La section comprend les bits de contrôle pour les IOBs en haut et en bas. L'outil génère le flux binaire partiel de ces colonnes, dans la même position qu'ils ont été dans le bitstream original[10].

- Dans le second, block mode, des lignes et des colonnes d'une zone rectangulaire à l'intérieur du FPGA sont spécifiées. Le bloc est alors visé comme région cible de la re-configuration partielle[10].

Outil de personnalisation de circuit

L'outil de personnalisation de circuit est un outil mis en œuvre dans l’architecture des circuits FPSLIC (Field Programmable System Level Integrated Circuit), qui sont des types FPGAs programmés par la société Amel. Ces circuits réunissent sur une puce complexe, un coeur de processeur standard avec ses mémoires, ses périphériques et l’habituel réseau logique programmable des FPGAs permettant la re-configuration en fonction des besoins de l’application[11]. Habituellement, un circuit FPGA a un ensemble de paramètres définissant son comportement, au cours de son chargement à partir d’une ROM externe. La fonction de cet outil est de simplifier la conception, le stockage des paramètres directement dans le flux binaire, sans utiliser la mémoire ROM ou des micro-contrôleurs externes. Les paramètres sont stockés en blocs de mémoire (SRAM) du circuit FPSLIC, ils sont ensuite modifiés par la re-configuration locale ou distante (à partir d'un serveur qui stocke le fichier de configuration). Cette approche réduit le coût global du système, car il élimine le besoin de dispositifs externes et / ou la logique de contrôle associée pour permettre le réglage des paramètres pendant l’exécution[11].

Il y a trois acteurs impliqués dans cet outil : le développeur du logiciel, le concepteur du circuit FPSLIC, et l'utilisateur du circuit.

- Le développeur du logiciel met en œuvre un logiciel layerhiding de détails d'architecture du FPGA. Cette couche logicielle est mise en œuvre sous forme d'applet. L'applet communique avec un serveur. Le serveur utilise des classes Jbits pour ouvrir / écrire et le flux de bits pour accéder et modifier les informations contenues dans le flux binaire. Cette applet est la même pour tous les circuits en cours d'adaptation[11].

- Le concepteur du circuit utilise des balises HTML pour passer des commandes et les paramètres à l'applet pour personnaliser son circuit. Dans la figure 10 : La référence à l'applet est dans la ligne 6 (BITGeneric.class). Le paramètre "path" (ligne 7) spécifie le nom de bitstream. Les paramètres "ip" et "port" (lignes 8 et 9) pour spécifier l'adresse IP du serveur et le service. Cela est nécessaire pour accéder à distance l'hôte connecté au FPGA. nbsignals paramètre indique le nombre de paramètres configurables (ligne 10)[11].

- Enfin, l'utilisateur du circuits FPSLIC reçoit la description HTML. La page de re-configuration qui en résulte est présentée dans la Figure 12. Dans la page de re-configuration, les valeurs des signaux peuvent être modifiées, enregistrées et les fichiers partiellement téléchargés dans le dispositif FPSLIC. Par conséquent, l'utilisateur peut alors résumer tous les détails concernant l’architecture, et effectuer une re-configuration à distance et partielle[11].

Bénéfices de la RTR

La RTR partielle ou globale permet d'une part, une meilleure exploitation du composant, une réduction de surface de silicium employé et donc du coût, et d'autre part, une évolutivité assurant la possibilité de couvrir à terme des besoins nouveaux sans nécessairement repenser à l'architecture dans sa totalité. L'un des points forts de la RTR est effectivement de permettre de reconfigurer en temps réel en quelques microsecondes tout ou une partie du circuit, c'est-à-dire permettre de modifier la fonctionnalité d'un circuit en temps quasi réel. Ainsi le même CLB pourra à un instant donné être intégré dans un processus de filtrage numérique d'un signal et l'instant d'après être utilisé pour gérer une alarme. On dispose donc quasiment de la souplesse d'un système informatique qui peut exploiter successivement des programmes différents, mais avec la différence fondamentale qu'ici il ne s'agit pas de logiciel mais de configuration matérielle, ce qui est infiniment plus puissant[1].

Auto-re-configuration

Les FPGAs sont capables de se reprogrammer dynamiquement indépendamment et sans aucune interaction nécessaire de l'homme. Les méthodes ou outils utilisés pour mettre en œuvre cette re-programmation dépendent des types de FPGAs et de leurs concepteurs.

Une conception qui met en œuvre l'auto-re-configuration est une étape importante pour la réalisation d'un système qui peut détecter des erreurs dans ses circuits et de reprogrammer les modules au besoin pour corriger ces erreurs.

La mise en œuvre d'un système auto-re-configurable exige un examen minutieux de plusieurs choix de conception importants. Les systèmes mettant en œuvre l'auto-re-configuration sont toujours rares dans la plupart des applications FPGA en raison de la surcharge relativement importante requise pour la phase d'analyse initiale et pour trouver un flot d’outil de travail[12].

En 2007, Xilinx a essayé de faire des systèmes partiellement auto-re-configurables plus faciles à mettre en œuvre. Bien qu'un flux d'outil plus standardisé et convivial pour l'auto-re-configuration partielle puisse être disponible bientôt, une grande quantité de recherche et d'essais a dû être utilisée afin d'atteindre un système d'auto-re-configurable en utilisant les outils et la documentation actuellement disponibles[12].

Auto-reconfiguration partielle

L’auto-re-configuration partielle est la possibilité de modifier la configuration d'une partie du FPGA par lui-même tandis que d'autres processus continuent de fonctionner. Différentes méthodes ont été proposées pour mettre en œuvre l’auto-re-configuration partielle notamment:- En utilisant les PowerPCs :

L'auto-re-configuration sur les FPGAs de type Xilinx Virtex est mis en œuvre en se servant du "Port d'Accès de Configuration Interne" (ICAP). Un bitstream partiel est écrit dans l'ICAP, ce bitstream reconfigure alors les parties spécifiées du FPGA avec la nouvelle logique. La communication avec l'ICAP peut être mise en œuvre par un PowerPC embarqué.

Un avantage significatif à l'utilisation du PowerPC, est que Xilinx a fourni une IP core qui s'interface avec l'ICAP. Une IP core représente une unité logique réutilisable ou un schéma de configuration qui est la propriété intellectuelle (IP) d'une société (ici c'est Xilinx). Grâce à cette interface, le PowerPC peut communiquer avec l'ICAP par de simples appels de méthodes, alors que la plupart des conceptions de l'interface de bas niveau sont cachées à l'utilisateur. En fait, une fois que le bitstream est chargé en mémoire, une seule méthode doit être appelée pour reprogrammer avec succès un module reconfigurable sur le périphérique[13].- En utilisant la compression et décompression des données de configuration (bitstream):

Toujours avec les FPGAs Xilinx Virtex. Lorsqu'un système utilise cette fonctionnalité avec de nombreux bitstreams de configuration pour le remplacement des parties à re-configurer dans la mémoire , la nécessité de la mémoire s’augmente. La somme des mémoires qui doit être fournie pour les données de configuration n'est pas négligeable. Ce fait suggère l'enquête de la compression des données avant qu'elles ne soient stockées dans des modules de mémoire d'un système. Les données compressées de bitstream doivent être décompressées avant de les transférer vers le FPGA[14].

La décompression est assurée par un module universel qui est capable de la réaliser au moment de l'exécution. Ce module pourrait être une partie d'un système d'exécution qui contrôle la décompression et qui reçoit les données pour la reconfiguration dynamique partielle. Les données décompressées sont ensuite transférées à l'interface de configuration du FPGA.

Les signaux internes de commande générés commencent la décompression des données de configuration stockées dans la mémoire externe. En connectant la sortie du décompresseur à l'interface de la zone de reconfiguration partielle, le système est capable de se reconfigurer[14].L'impact de la re-configuration dynamique

La reconfiguration dynamique permet d'augmenter l'efficacité d'un FPGA en allouant ses ressources logiques à plusieurs tâches[15]. Ainsi, en utilisant la notion de mémoire virtuelle qui permet entre autres d'exécuter un programme de taille plus grande que la mémoire physique disponible, un FPGA reconfigurable dynamiquement peut offrir une quantité importante de ressources logiques virtuelles et les mapper au moment de l'exécution sur une quantité réduite de ressources physiquement disponibles[15].

Un autre avantage qui suscite un intérêt croissant chez les chercheurs, est la flexibilité introduite par la reconfiguration dynamique des FPGA qui se manifeste à deux niveaux. Le premier niveau permet au concepteur, de facilement adapter son application pour faire face à de nouvelles contraintes ou pour remplacer un algorithme par un autre plus efficace. Cette flexibilité assure une certaine évolution du système[15]. Le second niveau se situe au choix des tâches à exécuter, qui peut se faire dynamiquement, par exemple en fonction des données à traiter. On peut donc tout à fait imaginer que les données d'entrée puissent influer en temps réel sur l'enchaînement des algorithmes. Le matériel devient extrêmement malléable et contrôlable par logiciel, il peut être utilisé à des instants différents pour exécuter des opérations différentes[15].

Théoriquement, la reconfiguration dynamique n'est pas réservée à une catégorie particulière de FPGA. Cependant, certains sont plus adaptés que d'autres pour satisfaire les contraintes temps réel. Le FPGA idéal pour construire un système reconfigurable dynamiquement doit posséder une vitesse d'exécution élevée et une durée de reconfiguration très faible[15]. Malheureusement, les FPGAs commercialisés à l'heure actuelle ne réunissent que partiellement ces deux caractéristiques. Cependant, un FPGA offrant une seule des deux caractéristiques sans que la deuxième ne soit excessivement pénalisante, peut être utilisé efficacement pour construire un système dynamique[15].

La durée de re-configuration a aussi un impact sur les performances d'un système dynamique, particulièrement si la modification de la fonctionnalité intervient fréquemment[15]. La meilleure utilisation d'un FPGA dans un système dynamique est alors de servir de coprocesseur à une machine hôte pour accélérer des traitements répétitifs sur un volume de données important[15].Exemple d'application des FPGA

Ici on parle d'une architecture qui met en œuvre des FPGAs dans une application de traitement d'images. L'architecture s'appelle ARDOISE. L’ambition d’ARDOISE est de pouvoir enchaîner les exécutions d’un flot d’algorithmes de segmentation d’images sur une même structure physique. Tout en reconfigurant plusieurs fois les FPGA au cours du traitement d’une même image[4].

On commence par étudier la zone re-configurable dynamiquement et son fonctionnement. Ce fonctionnement nécessite un contrôleur ce qui justifie l'architecture finale d'ARDOISE qui est abordée dans la suite[16].- Architecture de la zone re-configurable

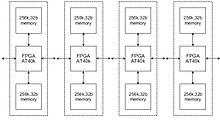

La partie re-configurable dynamiquement d'ARDOISE est constituée de 3 modules (ou plus) identiques appelés cartes filles. Une carte mère dont l'utilité et la structure seront décrites ultérieurement s'ajoute aux cartes filles. Voir la figure 12 [16].

On peut interconnecter jusqu'à 8 cartes filles. La figure 13 illustre quatre cartes filles interconnectées. Chacune des cartes filles est constituée d'un FPGA AT40k construit par la société ATMEL et de deux SRAM de 1MB[16]

.- Exemple de fonctionnement

Prenons trois cartes filles interconnectées pour réaliser des traitements d'image. On appelle UTGC (Unité de Traitement Grande Vitesse), la carte fille centrale. Les deux autres cartes filles sont les GTI (Gestionnaire de Tampon Image). on suppose qu'une image est présente dans la mémoire A. Une première configuration des FPGA permet de réaliser un premier traitement de cette image. Le résultat est stocké dans la mémoire C. On peut ensuite re-configurer l'architecture pour réaliser un traitement sur ce résultat. Le résultat du premier traitement est l'entrée du deuxième. La deuxième configuration prend donc ses entrées dans la mémoire C et stocke ses résultats dans la mémoire A. La figure 14 (A la fin de cette section) illustre cette explication. On peut réaliser plusieurs re-configurations en inversant à chaque fois le rôle des mémoires A et C[16].

Pendant que l'architecture est reconfigurée pour réaliser des calculs entre les mémoires A et C, on réalise l'acquisition d'une nouvelle image dans la mémoire B. Voir figure 15 (A la fin de cette section).

On est aussi en mesure de communiquer le résultat, stocké dans la mémoire D, de la série de traitements réalisés sur l'image précédente. Tant que ces deux opérations ne sont pas terminées, on dispose de temps pour reconfigurer l'architecture. Après cela, on dispose d'une nouvelle image dans la mémoire B, et le résultat des différentes configurations est stocké dans la mémoire C, on est alors en mesure de reprendre le processus en inversant le rôle des mémoires nord et sud. Une fois ce processus terminé, on se retrouve dans l'état initial. Une image est stockée dans la mémoire A, un résultat dans la mémoire C. On peut recommencer le cycle[16].

Le découplage des flux de données permet d'adapter la fréquence de traitement à chaque configuration. Le temps gagné en utilisant la fréquence maximum autorisée par la première configuration permet, grâce à la re-configuration dynamique, de réaliser plusieurs traitements sur les mêmes matérielles[16]

.- Description de l'architecture ARDOISE

Pour mettre en œuvre la re-configuration dynamique des cartes filles, il est nécessaire de se synchroniser sur le flux vidéo et de séquencer les phases de re-configuration et de calcul. Ces opérations peuvent être intégrées à la zone re-configurable dynamiquement en figeant une partie de cette zone. Pour le faire, on peut utiliser la re-configuration partielle des FPGA. Néanmoins, il est beaucoup plus commode d'ajouter un contrôleur de configuration. Le séquencement des re-configurations est donc confié, dans l'architecture ARDOISE à la carte mère. Pour réaliser cette opération efficacement la carte mère dispose de[16]:.

- une mémoire SRAM pour stocker les fichiers de configuration de la zone re-configurable dynamiquement en attendant de la reconfigurer[16].

- un circuit d'horloges programmables afin d'adapter la fréquence de traitement à chacune des configurations qui prennent place dans la zone re-configurable [16].

- un FPGA reconfiguré statiquement qui peut soit contrôler l'architecture entière (SRAM, horloges et zone re-configurable dynamiquement) en mode autonome, soit jouer le rôle d'interface entre ces éléments et un processeur en mode supervisé[16].

- une mémoire FLASH qui contient la configuration du FPGA de la carte mère ainsi que les configurations les plus utilisées des cartes filles[16].Annexes

Références

- Les composants FPGAs

- Marc, page 12

- Brad, page 420

- Didier, page 1

- Brad, page 422

- Brad, page 423

- Brad, page 427

- FPGA Run-Time Reconfiguration: Two Approaches

- Brad, page 428

- Self-reconfigurable platform for cryptographic application

- Daniel, page 5

- Evan, page 22

- Evan, page 23

- Michael, page 1

- Lounis, page 44

- Traitement d'images

Bibliographie

- (en) Brad L.Hutchings et Michael J.Wirthlin, « Implementation Approches for reconfigurable logic applications », dans 5th International Workshop, FPL '95 Oxford, United Kingdom, vol. 975, septembre 1995, p. 420-431

- Lounis Kessal, Nicolas Abel et Didier Demigny, « Traitement temps réel des images en exploitant la reconfiguration dynamique : architecture et programmation », dans TSI, avril 2005, p. 41-58

- Marc LEGER, « Fiabilité des Reconfigurations Dynamiques dans les Architectures à Composants », dans Thèse d'état, vol. 192, mai 2009

- (en) Jim Burns, Adam Donlin, Satnam Singh et Mark de Wit, « A Dynamic Reconfiguration Run-Time System », dans IEEE sensors Journal, vol. 75, août 2002

- (fr) La reconfiguration dynamique d'un FPGA

- (en) Wang Lie et Wu Feng-yan, « Dynamic partial reconfiguration in FPGAs », dans Third International Symposium on Intelligent Information Technology Application, vol. 2, 2009, p. 445-448

- (en) Miguel L. Silva et Joao Canas Ferreira, « Exploiting dynamic reconfiguration of platform FPGAs:

Implementation issues », dans Parallel and Distributed Processing Symposium.20th International, vol. 8, juin 2006

- (en) Steve Wichman, Sammit Adyha, Rohan Ambli, Brad Alcorn, Dr.Daniel Connors et Daniel Fay, « Partial Reconfiguration Across FPGAs », dans International Conference on Military and Aerospace Programmable Logic Devices (MAPLD), vol. 11, septembre 2006

- Didier Demigny, Ryad Bourguiba, Lounis Kessal et Michel Leclerc, « La Reconfiguration dynamique des FPGA :Que doit-on en attendre ? », dans Dix-septième colloque GRETSI, Vannes, vol. 4, septembre 1999

- (en) Edson L.Horta, John W.Lockwood, David E.Taylor et David Parlour, « Dynamic Hardware Plugins in an FPGA with Partial Run-time Reconfiguration », dans 39th annual Design Automation Conference, 2002, p. 343-348

- (en) Vincenzo Rana, Marco Santambrogio, Donatella Sciuto, Boris Kettelhoit, Markus Koester, Mario Porrmann et Ulrich Ruckert, « Partial Dynamic Reconfiguration in a Multi-FPGA Clustered Architecture Based on Linux », dans Parallel and Distributed Processing Symposium.IEEE International, vol. 8, juin 2007

- (en) Florent Berthelot et Fabienne Nouvel, « Partial and Dynamic Reconfiguration of FPGAs: a top down design methodology for an automatic implementation », dans Emerging VLSI Technologies and Architectures, 2006. IEEE Computer Society Annual Symposium on, vol. 00, mars 2006

- (en) Michael Huebner, Michael Ullmann, Florian Weissel et Juergen Becker, « Real-time Configuration Code Decompression for Dynamic FPGA Self-Reconfiguration », dans Parallel and Distributed Processing Symposium, 18th International, vol. 6, avril 2004

- (en) Salih Bayar et Arda Yurdakul, « Self-Reconfiguration on Spartan-III FPGAs with Compressed Partial Bitstreams via a Parallel Configuration Access Port (cPCAP) Core », dans Research in Microelectronics and Electronics. PRIME 2008. Ph.D., Avril-Juin 2008

- (en) Daniel Mesquita, Fernando Moraes, José Palma, Leandro Möller et Ney Calazans, « Remote and Partial Reconfiguration of FPGAs: tools and trends », dans Parallel and Distributed Processing Symposium, vol. 8, avril 2003

- (en) Evan Custodio et Brian Marsland, « Self-Healing Partial Reconfiguration of an FPGA », dans Project Number:MQP-BYK-GD07 Submitted to the Faculty of the WORCESTER POLYTECHNIC INSTITUTE in partial fulfillment of the requirements for the

Degree of Bachelor of Science, avril 2007

Autres Références Bibliographiques

- (en) Tamas Raikovich, « Dynamic Reconfiguration Of FPGA Devices », dans 15th PhD Mini-symposium. Budapest, Hungary, vol. 2, février 2008, p. 72-73

- (en) Neil W. Bergmann, Yi Lu et John A. Williams, « Automatic Self-Reconfiguration of System-on-Chip Peripherals », dans International Symposium on Field-Programmable Custom Computing Machines, 2007

- Ryad Bourguiba, Lounis Kessal et Didier Demigny, « Reconfiguration dynamique des FPGA pour une segmentation d’image adaptative et temps réel », dans Seizième colloque Grenoble, septembre 1997

- (fr) Circuits reconigurables: Les FPGAs

- (en) Partial Reconfiguration Across FPGAs

- (fr) Reconfiguration partielle

- (fr) Les circuits logiques programmables FPGA

- Portail de l’électricité et de l’électronique

- Portail de l’informatique

Wikimedia Foundation. 2010.