- Circuit asynchrone

-

Un circuit asynchrone est un circuit électronique qui n'utilise pas de signal d'horloge global pour synchroniser ses différents éléments. À la place, ceux-ci communiquent en indiquant localement quand des données sont disponibles.

Sommaire

Théorie

Les circuits asynchrones regroupent en fait plusieurs classes de circuit ayant des propriétés différentes, selon les hypothèses faites à la conception :

- Insensibles aux délais : ces circuits fonctionnent correctement quels que soient les délais dans les fils et les portes. Ils ne sont cependant pas réalisables avec des portes logiques simples (les seules portes logiques à une sortie utilisables sont les portes C et l'inverseur)[1], et ne sont donc pas souvent utilisés en pratique. Ce modèle est cependant utilisable avec des portes plus complexes.

- Quasi-insensibles aux délais : ces circuits ajoutent simplement l'hypothèse, pour la conception, qu'il est possible d'obtenir des fourches isochrones, c'est-à-dire deux fils induisant exactement le même délai. Tout comme le modèle suivant, c'est un modèle de conception largement utilisé pour des processeurs asynchrones.

- Indépendants de la vitesse : ici, on considère les délais dans les fils comme étant négligeables, ce qui est une hypothèse encore plus forte que celle de quasi-insensibilité aux délais. Cela se vérifie difficilement dans les systèmes actuels, c'est pourquoi on peut leur préférer des circuits conçus comme quasi-insensibles aux délais. Cependant, les deux hypothèses sont en fait très proches en termes de conséquences, le cas indépendant de la vitesse se ramenant en fait au cas où toutes les fourches sont isochrones.

- À délais bornés : les délais dans les portes et les fils sont supposés bornés par une durée connue. C'est le principe de conception en électronique synchrone, où les impulsions d'horloge se font à intervalle suffisamment long pour que les signaux se soient propagés dans tout le circuit et stabilisés. En électronique asynchrone, ce modèle est peu utilisé, si ce n'est pour concevoir la structure interne de certaines portes.

Comme chaque partie du circuit est indépendante, ils se prêtent bien à la modélisation mathématique, par exemple par des méthodes proches des réseaux de Petri.

Caractéristiques

Vitesse

D'une part, les circuits permettant de passer des données d'un élément à l'autre introduisent une latence supplémentaire, chaque élément comprenant généralement plusieurs bascules et verrous pour cela. Par contre, il n'est pas limité par un signal d'horloge global, et la vitesse n'est pas forcément la même selon les parties ou les données en entrée. Par exemple, pour des additionneurs, certaines implémentations asynchrones peuvent renvoyer le résultat dès qu'il est calculé, alors qu'un circuit synchrone doit toujours attendre jusqu'au signal d'horloge suivant (qui doit être suffisamment tard pour que les calculs soient terminés même dans le pire des cas). Ils permettent donc de bonnes implémentations en temps moyen de calcul, même si le pire des cas peut être bien plus long.

Consommation d'énergie

Les circuits asynchrones ne sont actifs que lorsque des données sont disponibles. Dans le cas contraire, ils ne consomment que la puissance due au courant de fuite des transistors, ce qui en fait des candidats crédibles pour des circuits à basse consommation, ou lorsque la charge de travail évolue rapidement. Cependant, pour assurer la communication entre les éléments, ils utilisent aussi plus de transistors que leurs équivalents synchrones, ce qui peut compenser les gains potentiels et qui augmente la taille des puces.

Modularité

Il est facile d'utiliser ensemble des circuits asynchrones différents, car aucun élément n'a besoin d'être commun, au contraire de l'horloge des circuits synchrones. C'est un avantage pour la communication avec d'autres éléments, mais aussi pour la conception, qui peut se faire de manière modulaire.

Émissions électromagnétiques

Du fait que les différents éléments ne sont pas synchronisés, les émissions électromagnétiques sont réduites tandis que la consommation électrique est lissée. Un circuit synchrone, a contrario, a tendance à émettre des ondes harmoniques de sa fréquence d'horloge et à présenter des pics de puissance consommée à chaque front d'horloge.

Protocoles de communication

Entre deux éléments d'un circuit asynchrone échangeant des données, on considère une communication à sens unique entre un émetteur et un destinataire. Il existe de nombreux moyens de la réaliser de manière fiable, mais seuls quelques-uns sont utilisés en pratique : lorsque ses données sont prêtes, l'émetteur les rend disponibles en sortie et en informe le destinataire ; celui-ci, lorsqu'il peut accepter les données (quand il a transmis ou utilisé les données précédentes), les copie, puis renvoie un signal via un second fil destiné aux réponses, appelé signal d'acquittement.

Protocole

On distingue deux protocoles, selon la façon dont le signal d'acquittement est codé :

- soit elle correspond à une transition quelconque, de 1 à 0 ou de 0 à 1. On parle de protocole à deux phases, de "half-handshake" ou de codage NRZ (Non-return-to-zero).

- soit le destinataire signale par une transition non seulement la réception des données, mais aussi la détection du passage par un état invalide : au cycle suivant, le signal d'acquittement est donc revenu à son état initial. On parle de protocole à quatre phases, de "full-handshake" ou de codage RZ (Return-to-zero). Malgré une apparente complexité, ce protocole permet des implémentations souvent plus simples et rapides que le protocole à deux phases.

Codage des données

Codage à données groupées

Dans ce protocole, un ou plusieurs fils transportent les données, avec un fil par bit. Un fil (Req) est destiné à la requête de l'émetteur indiquant que les données sont prêtes, et un autre (Ack) à la réponse du destinataire.

On parle souvent de micropipeline pour désigner les circuits utilisant ce codage, avec soit deux soit quatre phase. A l'origine, ce terme fait référence à un pipeline asynchrone utilisant un protocole 2 phases données groupées[2].

Codage double-rail

Ici, les données et la requête sont encodés ensemble sur deux fils, la requête étant implicite lors des transitions sur ceux-ci. L'acquittement se fait via un troisième.

Deux protocoles sont largement répandus, utilisant soit trois, soit quatre états.

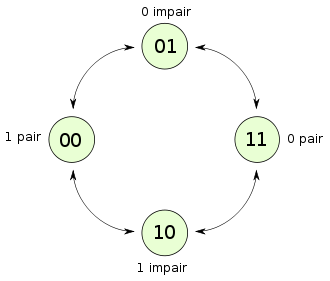

- Codage quatre états

Ici, tous les états sont signifiants, mais deux codes correspondent à chaque valeur d'un bit, ce qui permet bien de changer d'état à chaque nouvelle donnée. Ce codage est bien adapté à un protocole à deux phases.

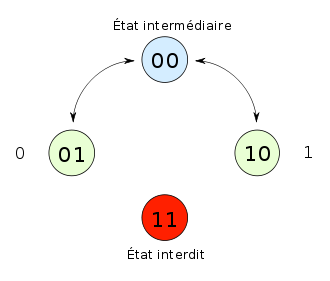

- Codage trois états

Le codage utilisé ici comporte une valeur invalide (typiquement 00), et deux valeurs signifiantes (01 codant 0 et 10 codant 1 par exemple). L'état 11 est inutilisé. L'émetteur repasse par l'état invalide à chaque envoi de données. Pour signifier que le destinataire a remarqué le changement de valeur, une réponse est émise à chaque fois, y compris au passage par l'état invalide. Ce protocole comporte donc quatre phases.

Portes pour l'électronique asynchrone

Pour simplifier la création d'éléments asynchrones, plusieurs portes de base sont utilisées, souvent basées sur la porte C de Muller. On peut créer des portes permettant d'envoyer une donnée reçue sur deux sorties simultanément, d'envoyer toutes les données reçues sur les entrées sur une unique sortie, ou de contrôler l'accès à des ressources partagées. On peut aussi obtenir des portes équivalentes aux portes synchrones, mais utilisant un protocole de communication asynchrone, tels que des portes OU ou des additionneurs. Le caractère modulaire des circuits asynchrones permet de les combiner facilement.

Les implémentations varient bien sûr selon le protocole utilisé, mais aussi selon les propriétés recherchées (faible latence, bande passante élevée, fiabilité, déterminisme, faible consommation): certaines portes vont pouvoir renvoyer un résultat sans attendre que toutes les entrées soient disponibles[3] (par exemple une porte OU si une entrée vaut 1), ou se focaliser sur des considérations de taille ou de consommation.

Mise en œuvre

Pour créer des portes logiques utilisant des protocoles de communication asynchrones, les méthodes diffèrent suivant le codage et le protocole. En particulier :

- les portes issues de la logique combinatoire peuvent être utilisées pour le codage à données groupées. Un délai doit alors être imposé au signal de requête de manière à ce qu'il arrive après la fin des calculs.

- les portes peuvent aussi indiquer par elles-mêmes la fin des calculs, ce qui est facile avec un codage double-rail. Cela évite de devoir ajouter un délai, et est aussi bien adapté pour créer des portes à complétion anticipée[4]. Ces techniques requièrent par contre plus de transistors.

Les bascules, quant à elles, sont réalisées avec des portes dédiées, et diffèrent fortement selon le protocole utilisé : un protocole double-rail à 3 états permet d'utiliser des bascules à base de portes C. Les protocoles à données groupées nécessitent des portes spécifiques.

Conception de circuits asynchrones

Langages

Comme les seules choses qui importent dans un circuit asynchrone sont les interactions entre les éléments, on peut concevoir les circuits à partir de langages de haut niveau, souvent dérivés du langage CSP, par exemple CHP et Occam. Il est aussi possible d'utiliser des langages de description matérielle plus classiques, comme Verilog ou VHDL, qui ne sont pas spécifiquement destinés à la conception de circuits asynchrones.

Problèmes liés à la conception

La conception de circuits asynchrones souffre d'un manque d'outils dédiés, les principaux langages de description de matériels privilégiant les circuits synchrones. Cependant, il est possible d'utiliser ceux-ci pour dessiner des circuits asynchrones.

Le deuxième problème tient à la formation de ceux qui dessinent ces circuits, qui est généralement focalisée sur l'électronique synchrone, l'électronique asynchrone étant moins répandue et souvent vue comme moins efficace ou plus complexe.

Notes et références

- (en) Alain J. Martin, The limitations to delay insensitivity in asynchronous circuits, janvier 1990 [lire en ligne]

- (en) Ivan E. Sutherland, Micropipelines, juin 1989 [lire en ligne]

- (en) Charlie Brej, Early output logic and anti-tokens, septembre 2005 [lire en ligne]

- (en) Charlie Brej, Asynchronous early output and early acknowledge dual-rail protocols, octobre 2002 [lire en ligne]

Voir aussi

Articles connexes

Bibliographie

- Pascal Vivet, Une méthodologie de conception de circuits intégrés quasi-insensibles aux délais : application à l'étude et à la réalisation d'un processeur RISC 16-bit asynchrone, 21 juin 2001 [lire en ligne]

- (en) Jens Sparsø, Asynchronous circuit design : A tutorial [lire en ligne]

- (en) Nigel Charles Paver, The design and implementation of an asynchronous microprocessor, 1994 [lire en ligne]

- Portail de l’électricité et de l’électronique

Wikimedia Foundation. 2010.