- Tampon trois etats

-

Tampon trois états

En électronique, on appelle étage tampon un étage qui est caractérisé par une impédance d'entrée élevée et une impédance de sortie faible. On parlera aussi d'étage adaptateur d'impédances.

On distingue trois types de circuits : les tampons, les tampons 3 états et les circuits d'interface.

Tampons

Symbole et table de vérité d'un étage tampon

Symbole et table de vérité d'un étage tamponDans le domaine de l'électronique numérique, un tampon est simplement un circuit non inverseur à une entrée et une sortie. L'état logique de la sortie est égal à celui de l'entrée. Remarquons toutefois qu'au moment des changements d'état, il s'écoule toujours un certain temps (appelé temps de propagation, tp) entre le moment où l'entrée et la sortie changent d'état. Le symbole et la table de vérité sont donnés dans la figure ci-contre.

On appelle sortance d'un circuit intégré numérique le nombre d'entrées de circuits de même technologie que l'on peut raccorder à une même sortie. Cette sortance est en pratique de l'ordre de 10, même si certaines technnologies, comme les circuits CMOS, affichent des valeurs bien supérieures.

Le circuit tampon est utilisé :

- lorsqu'une sortie doit piloter un nombre d'entrées supérieur à sa sortance ; exemple : si une sortie doit piloter 15 entrées, on placera deux étages tampons, dont l'entrée est pilotée par la sortie ; l'un pilotera 8 entrées, l'autre 7 ;

- lorsque l'on mélange des circuits de technologies différentes ; ainsi, une sortie de circuit NMOS ne peut piloter que 2 entrées TTL ; l'utilisation d'un étage tampon est donc nécessaire dès que l'on dépasse ce nombre.

Des étages tampons sont très souvent utilisés dans les circuits à microprocesseur. En effet, les bus d'adresses et de données du microprocesseur sont reliés aux mémoires, aux ports d'entrée et de sortie, et aux différents périphériques du système, ce qui multiplie le nombre d'entrées pilotées.

Remarque : les tampons utilisés pour le bus de données doivent être bidirectionnels, ce qui nécessite l'utilisation de tampons 3 états.

Tampons 3 états

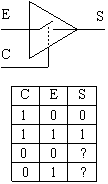

Symbole et table de vérité d'un tampon 3E

Symbole et table de vérité d'un tampon 3EUn tampon 3 états est un tampon doté d'une deuxième entrée, appelée entrée de commande C. Lorsque cette entrée est au niveau actif (par exemple, 1), le tampon se comporte normalement : la sortie S reflète l'état de l'entrée E. Si C est au niveau inactif, la sortie est isolée de l'entrée, son niveau logique étant indéterminé ou défini par un autre élément du système (résistance de rappel à la masse ou à Vcc, autre circuit, etc.). Le symbole et la table de vérité sont donnés dans la figure ci-contre.

Le rôle fondamental du tampon 3 états est donc un rôle d'isolement. Il est équivalent à un interrupteur qui est ouvert ou fermé selon le niveau logique appliqué à l'entrée de commande.

Les tampons 3 états sont indispensables dans les systèmes à microprocesseur (MP). Ils sont le plus souvent intégrés dans les circuits destinés à être raccordés au bus de données du MP. Pour relier à un même bus différents boîtiers mémoire sans que ceux-ci ne se disputent le contrôle du bus, il suffit de placer sur chaque sortie de chaque boîtier un tampon 3 états. Lorsque le microprocesseur veut lire une donnée provenant d'un boîtier, il sélectionne ce boîtier (à l'aide du bus d'adresses et d'un décodeur) et rend ses tampons passants ; tous les autres boîtiers mémoire sont isolés du bus par leurs propres tampons, qui seront isolants tant que l'on n'a pas besoin de l'un d'entre eux.

Remarques :

- on peut utiliser un tampon 3 états comme un tampon normal, en connectant l'entrée C en permanence au niveau actif ;

- une petite difficulté se pose lorsque l'on veut piloter le bus de données d'un MP par un étage tampon externe ;

le bus de données est bidirectionnel : à certains moments les données se propagent des mémoires et périphériques vers le MP, à d'autres, dans le sens MP vers mémoires ou périphériques. Il est donc nécessaire de placer sur chaque ligne du bus 2 tampons 3 états en sens opposés ; les signaux de lecture et d'écriture du MP sont utilisés pour rendre les tampons passants aux moments adéquats.

Circuits d'interface

Les circuits d'interface peuvent également être considérés comme des circuits tampons, dans la mesure où ils présentent une impédance d'entrée élevée et une impédance de sortie faible. Mais leur rôle est de servir de traducteur de niveau : ils sont utilisés lorsque l'on combine au sein d'un même système des circuits intégrés de technologies différentes, caractérisés par des niveaux logiques différents.

Exemple : on veut raccorder la sortie d'un diviseur de fréquence en technologie ECL à un compteur CMOS. Le problème, c'est qu'en général les circuits ECL sont alimentés par une alimentation négative de -5,2 V, et que les niveaux logiques sont -0,8 et -1,7 V. Ce qui n'est pas compatible avec un circuits CMOS, alimenté en 5 V et acceptant des niveaux logiques de 0 à 2 V pour un 0, et de 3 à 5 V pour un 1. La solution est de placer entre ces deux circuits un circuit d'interface qui « parle » ECL à son entrée, et qui « parle » TTL à sa sortie.

Remarquons que les circuits d'interface, comme d'ailleurs les tampons, sont aussi disponibles en version inverseur.

- Portail de l’électricité et de l’électronique

Catégorie : Circuit électrique

Wikimedia Foundation. 2010.